组合逻辑

组合逻辑是Verilog HDL设计中的一个重要组成部分。从电路的本质上来讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关,无存储电路,也没有反馈电路。

多路选择器

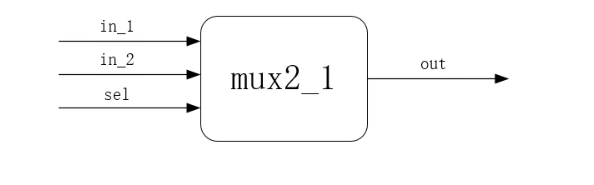

多路选择器是数据选择器的别称,在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称为多路选择器或多路开关。

原理框图

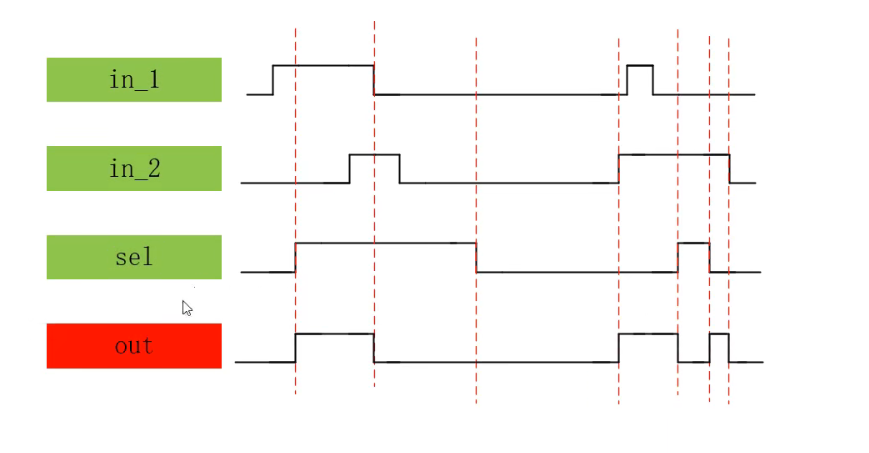

波形图

代码部分

// Filename﹕ mux2_1.v

// Author﹕YMY

// Description﹕多路选择器模块

// Calledby﹕/

// RevisionHistory﹕22-03-31

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

module mux2_1(

input wire in_1 ,//输入信号1

input wire in_2 ,//输入信号2

input wire sel ,//选通信号

output reg out //输出信号

);

always @(*) begin //* 表示只要由信号变化就会执行

if(sel == 1'b1)

begin

out = in_1; //如果选通信号为高电平,将输入信号1赋值给输出信号

end

else

begin

out = in_2; //否则选通信号为低电平,将输入信号2赋值给输出信号

end

end

endmodule

endmodule

仿真代码

// Filename﹕ tb_mux2_1.v

// Author﹕YMY

// Description﹕多路选择器模块测试

// Calledby﹕/

// RevisionHistory﹕22-03-31

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

module tb_mux2_1();

reg in_1; //输入信号1

reg in_2; //输入信号2

reg sel ; //选通信号

wire out ; //输出信号

//初始化信号

initial begin

in_1 <= 1'b0;

in_2 <= 1'b0;

sel <= 1'b0;

end

//产生随机数,%2 产生的非随机数为0或者1

always #10 in_1 <= {$random}%2;

always #10 in_2 <= {$random}%2;

always #10 sel <= {$random}%2;

initial begin

//设置时间格式的系统函数

$timeformat(-9,0,"ns",6); //-9 10^-9表示ns ,0 表示小数位数,6表示打印的最下数字字符是6个

//检测打印函数

$monitor("@time %t:in_1=%b in_2=%b sel=%b out=%b",$time,in_1,in_2,sel,out); //%b二进制数

end

//模块例化

mux2_1 mux2_1_inst

(

. in_1 (in_1),//输入信号1

. in_2 (in_2),//输入信号2

. sel (sel ),//选通信号

. out (out ) //输出信号

);

endmodule

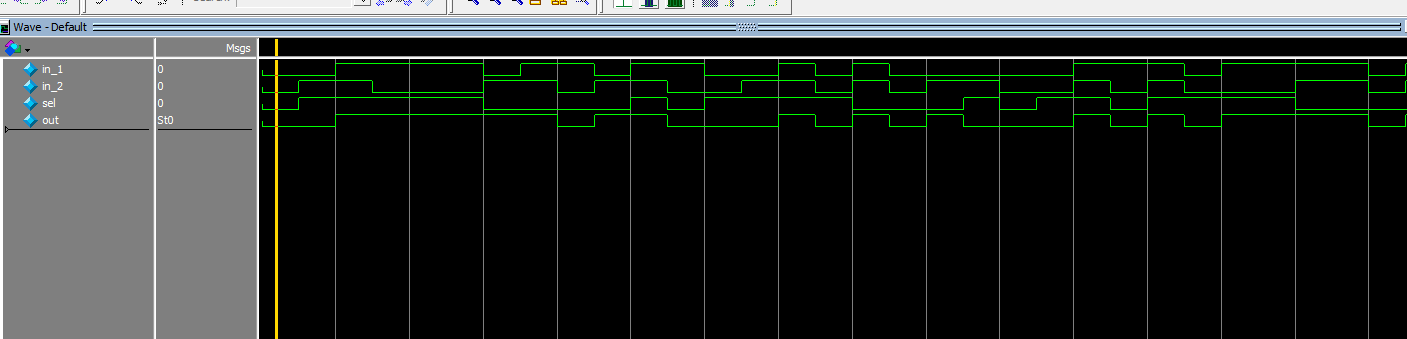

仿真波形