组合逻辑电路&时序逻辑电路

组合逻辑电路:

任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

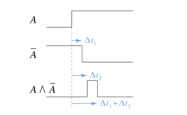

竞争与冒险:

当一个逻辑门的两个输入信号同时向相反方向变化时,从变化开始达到稳定状态所需要的时间不同,称为竞争。

逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲的现象,称为冒险。

竞争与冒险的消除方法:

加封锁脉冲。在输入信号产生竞争与冒险的时间内,引入一个脉冲将可能产生尖峰干扰脉冲的门封锁住。封锁脉冲应在输入信号转换前到来,转换结束后消失。

加选通脉冲。对输出可能产生尖峰干扰脉冲的门电路增加一个接选通信号的输入端,只有在输入信号转换完成并稳定后,才引入选通脉冲将它打开,此时才允许有输出。在转换过程中,由于没有加选通脉冲,因此,输出不会出现尖峰干扰脉冲。

接入滤波电容。由于尖峰干扰脉冲的宽度一般都很窄,在可能产生尖峰干扰脉冲的门电路输出端与地之间接入一个容量为几十pf的电容就可吸掉尖峰干扰脉冲。

修改逻辑设计。

如果布尔式中有相反信号,则可能产生竞争与冒险。解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

常见的组合逻辑电路:多路选择器、编码器、译码器、移位器、比较器。

多路选择器:最简单的多路选择器(Multiplexer)是1位二选一多路器。

当输入S为高电平时,输出Y的值为输入A1的值;当输入S为低电平,输出Y的值为A0;

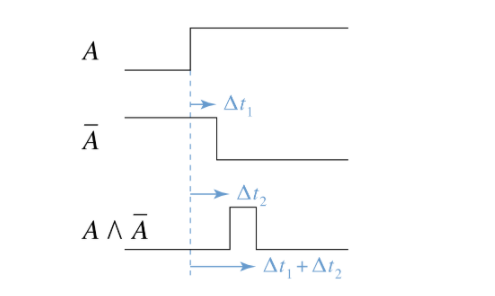

编码器 :具有编码功能的逻辑电路。

比较器 :把比较器输入信号之间是否相等的电路叫做比较器(Comparator):如果两个输入向量相等,则输出高电平,否则输出低电平。

译码器:译码是编码的逆过程,译码器可以将输入二进制代码的状态翻译成输出信号。

移位器:一种移位信号作用下使数据逐位移动的组合电路。

时序逻辑电路 :

输出不仅取决于当前的输入,还取决于电路的历史状态。

典型的时序逻辑电路:计数器、寄存器、触发器

常见的时序逻辑元件:锁存器、触发器

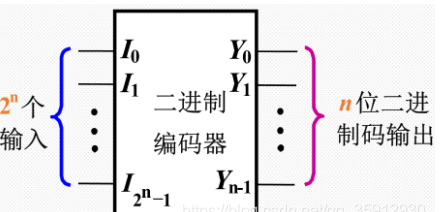

锁存器:锁存器在E的高(低)电平期间对信号敏感。对脉冲电平敏感的存储电路,在特定输入脉冲电平作用下改变状态。

触发器:触发器在CP的上升沿(下降沿)对信号敏感。对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

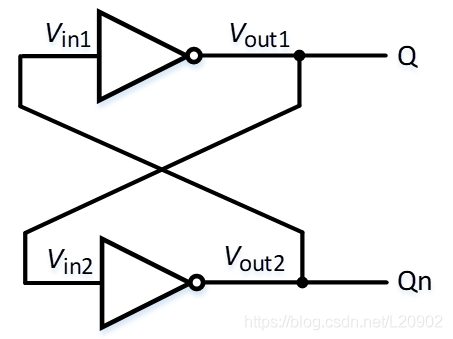

锁存器,最简单的时序由一对反相器形成一个双稳态元件

若Q为高电平输出,则Vin2为高电平输入,Qn输出低电平,同时Vin1也为低电平输入。又使得Q继续保持高电平输出;

若Q为低电平输出,则Vin2位低电平输入,Qn输出高电平,同时Vin1也为高电平输入,又使得Q继续保持低电平输出。

D触发器:在时钟信号上升沿或者下降沿时,保持输入信号状态,改变输出信号的触发器。

同步逻辑和异步逻辑

同步逻辑:是时钟之间有固定的因果关系。

异步逻辑:是各时钟之间没有固定的因果关系。

同步电路和异步电路

同步电路:利用时钟脉冲使其子系统同步运作。是由时序和组合逻辑过程的电路,其操作都是在严格的时钟控制下完成的。

异步电路不使用时钟脉冲做同步。主要是组合逻辑电路,用于产生地址译码器,FIFO、RAM的读写控制脉冲。

如何解决亚稳态

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

解决方法:

1. 降低系统时钟

2. 用反应更快的触发器Flip_Flop

3. 引入同步机制,防止亚稳态传播

4. 改善时钟质量,用边沿变化快速的时钟信号

本文 zblog模板 原创,转载保留链接!网址:http://xn--zqqs03dbu6a.cn/?id=29

1.本站遵循行业规范,任何转载的稿件都会明确标注作者和来源;2.本站的原创文章,请转载时务必注明文章作者和来源,不尊重原创的行为我们将追究责任;3.作者投稿可能会经我们编辑修改或补充。