一、实验目的

实现在线调试FPGA的IP核ILA,在FPGA运行的时候抓取逻辑信号波形做分析。

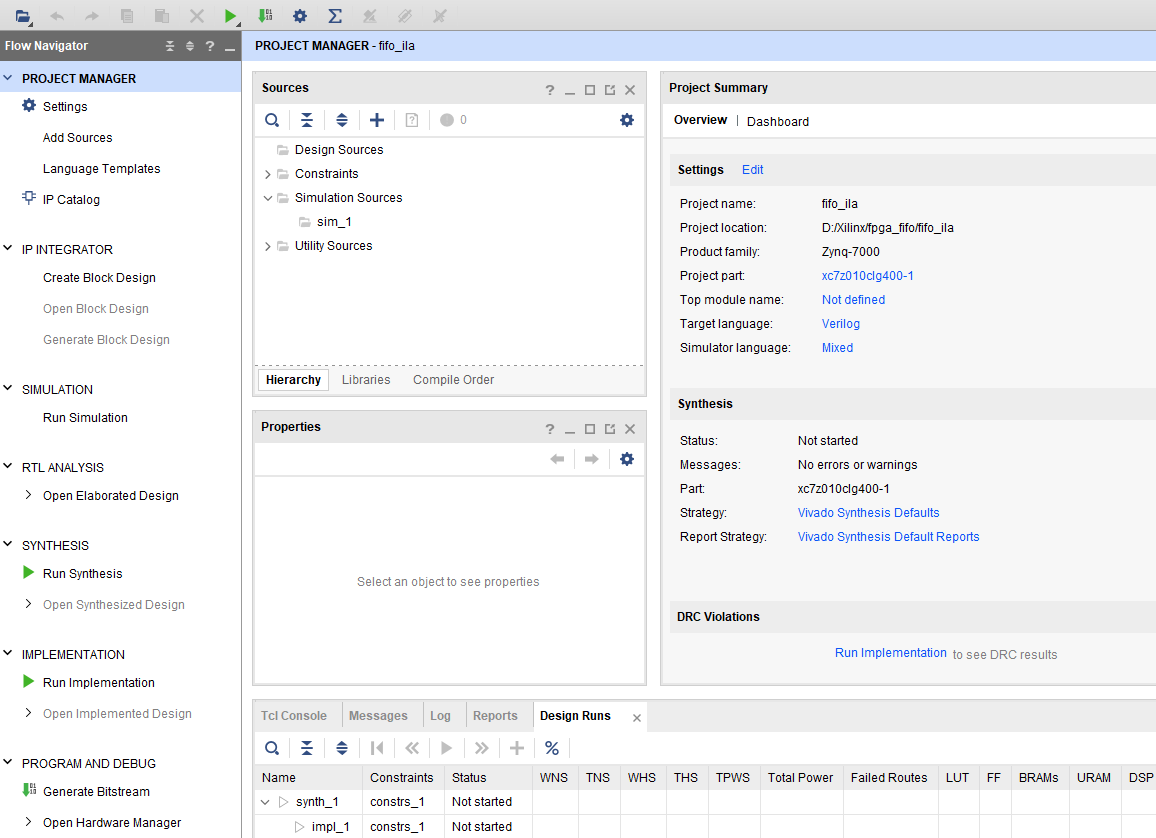

二、ZYNQ工程建立

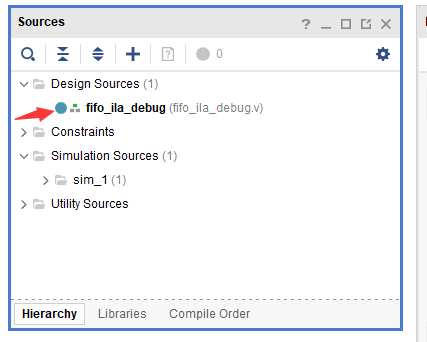

三、新建Verilog文档

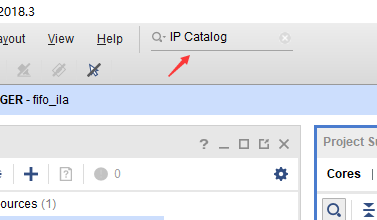

搜索 IP Catalog

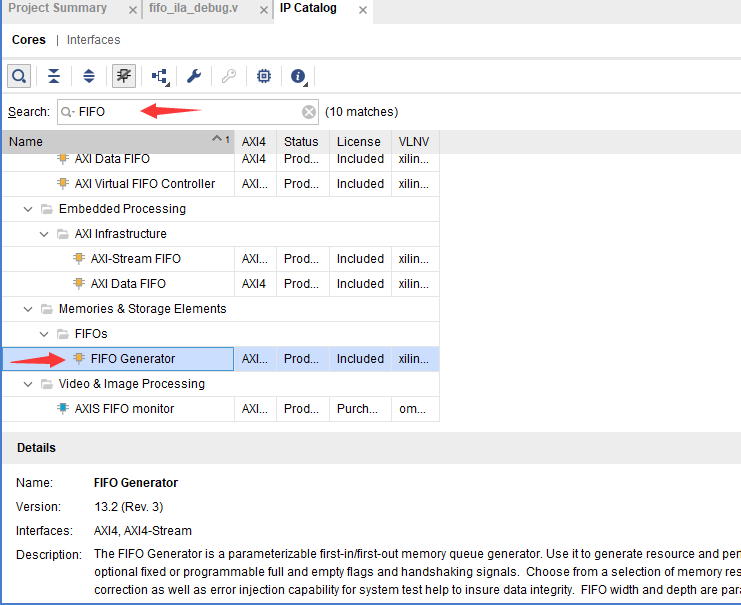

调用一个FIFO的IP

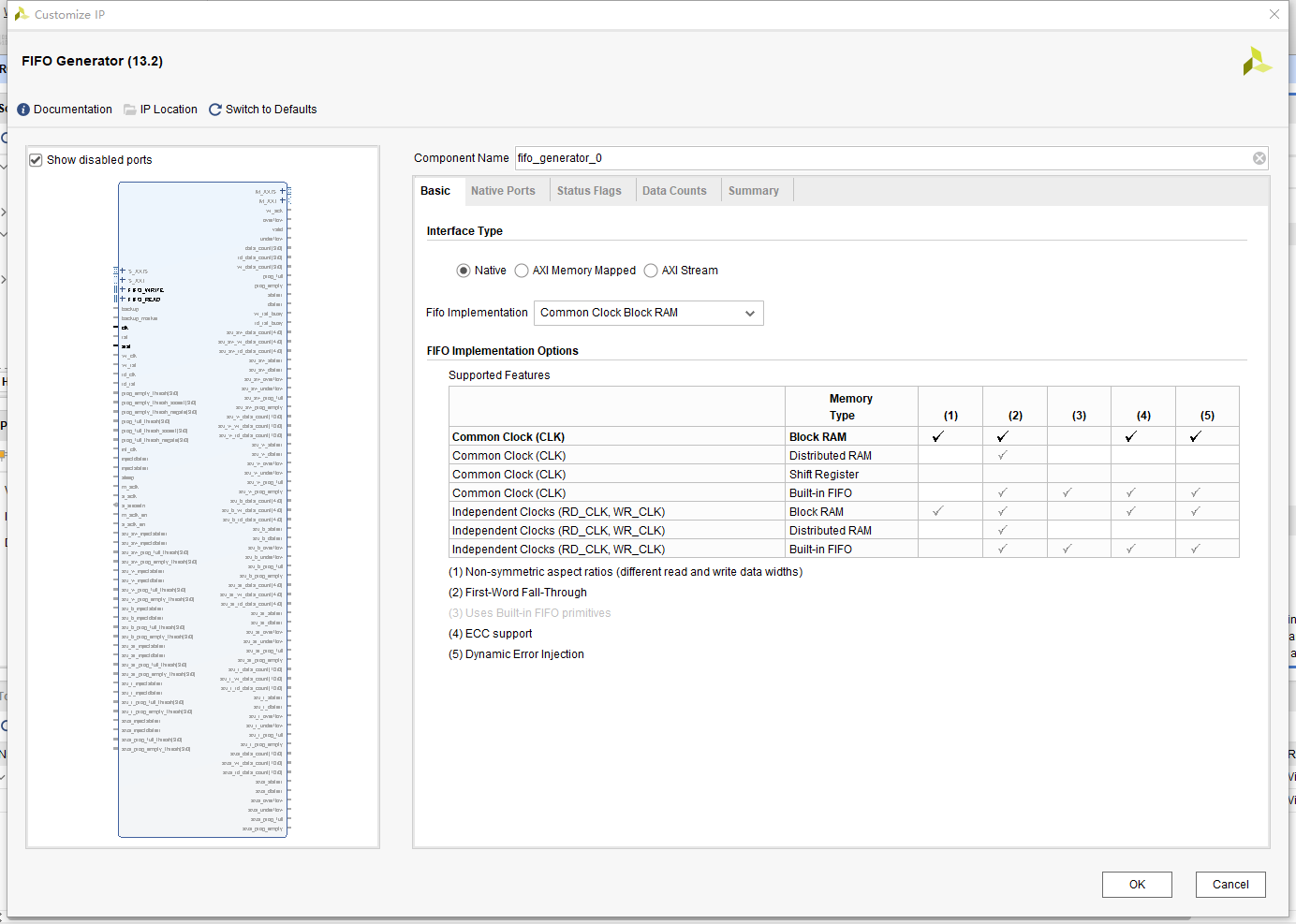

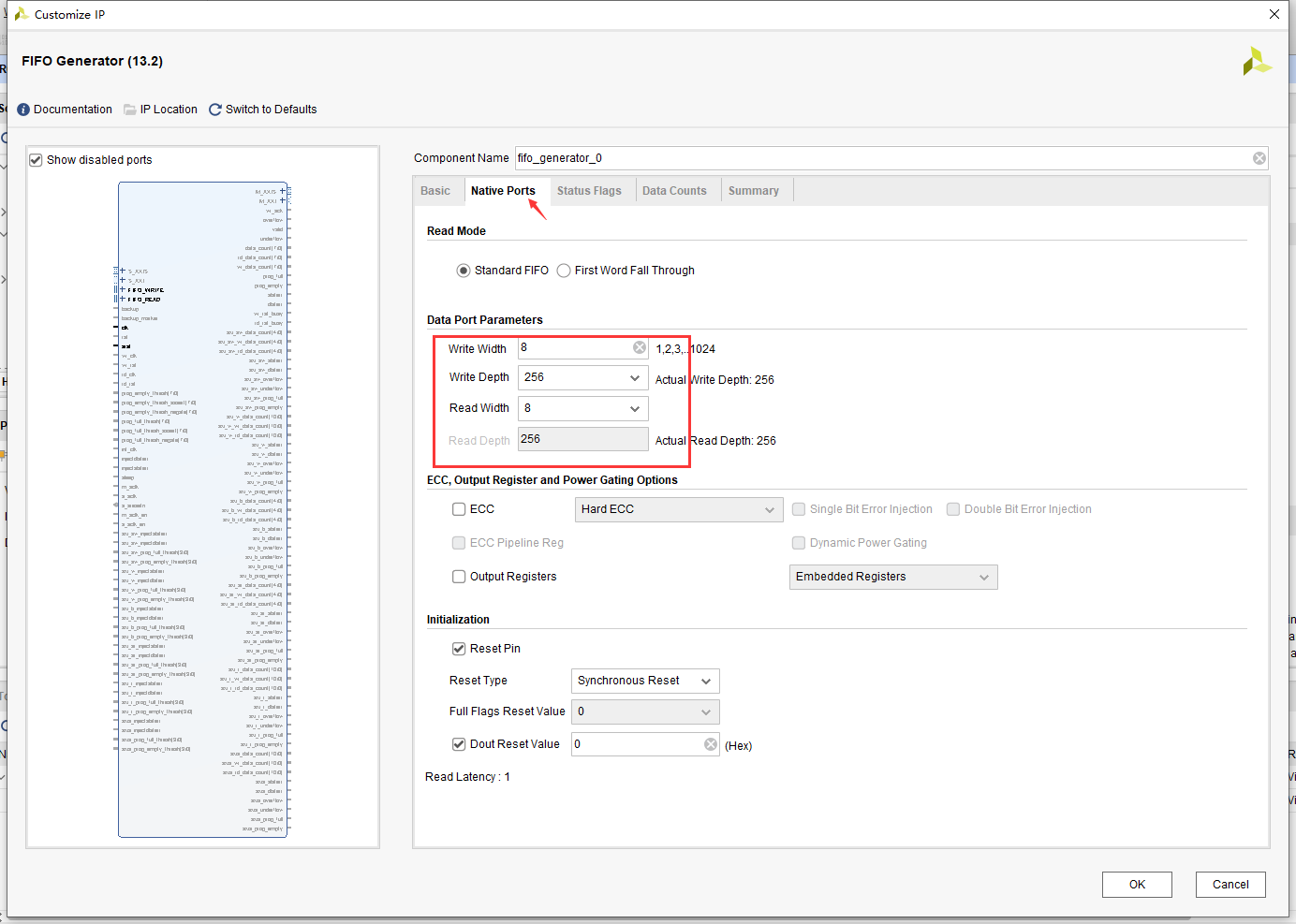

双击,进行FIFO配置,BASIC保持不变

Native Ports 修改如下,点击OK,生成IP

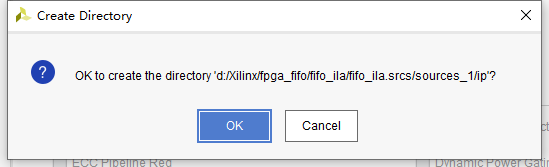

5. 点击OK

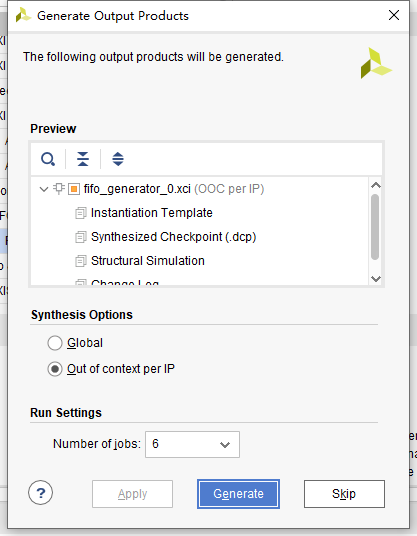

6. 点击generate

7. 点击OK

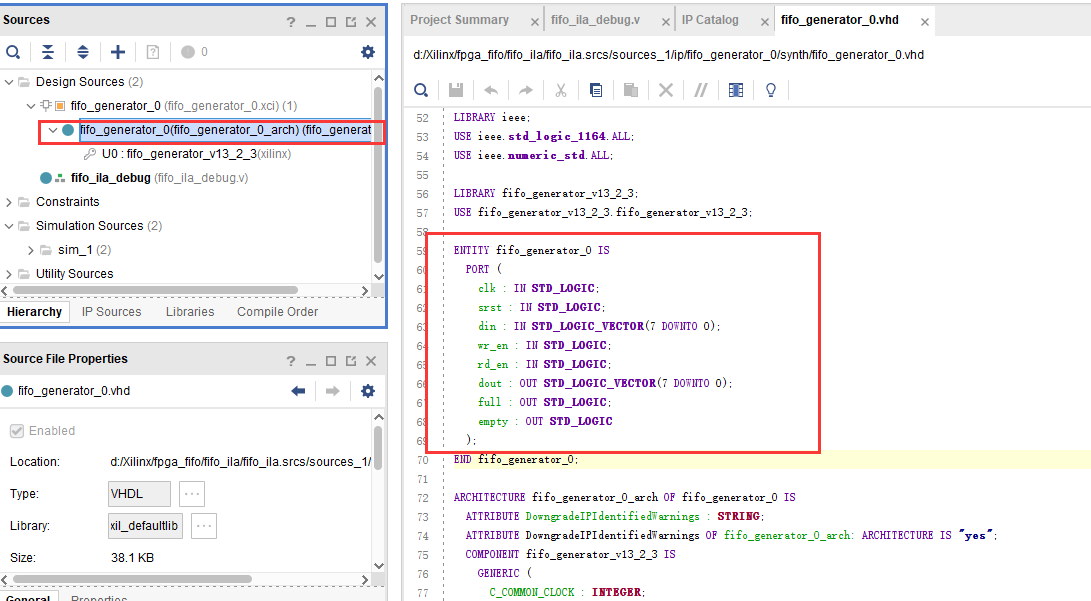

8. 我们点击IP核左边的箭头展开, 找到IP顶层文件双击打开,可以看到,这个FIFO的顶层代码为VHDL。

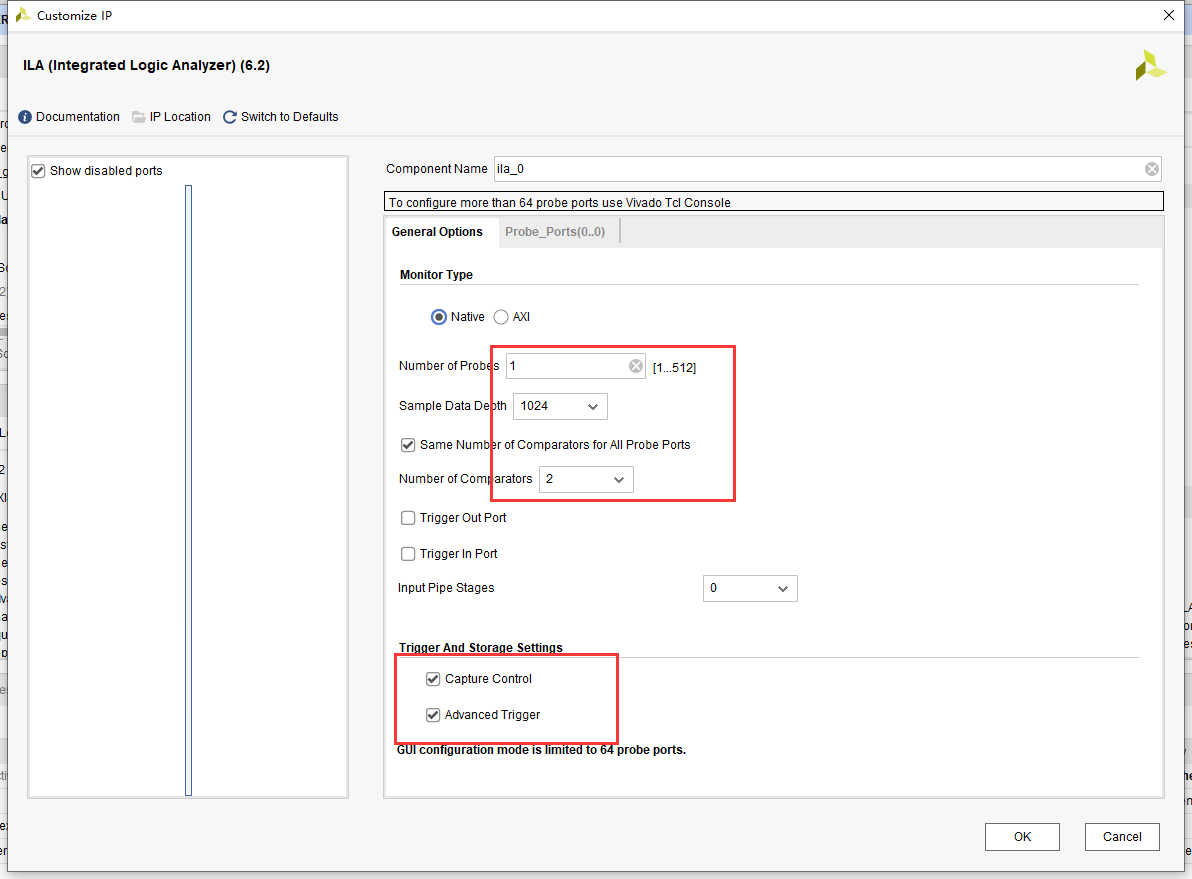

9. 接着我们添加ILA逻辑分析模块。点击IP Catalog,Search输入ILA,然后双击打开进行ILA 的配置工作

10 . General Option配置

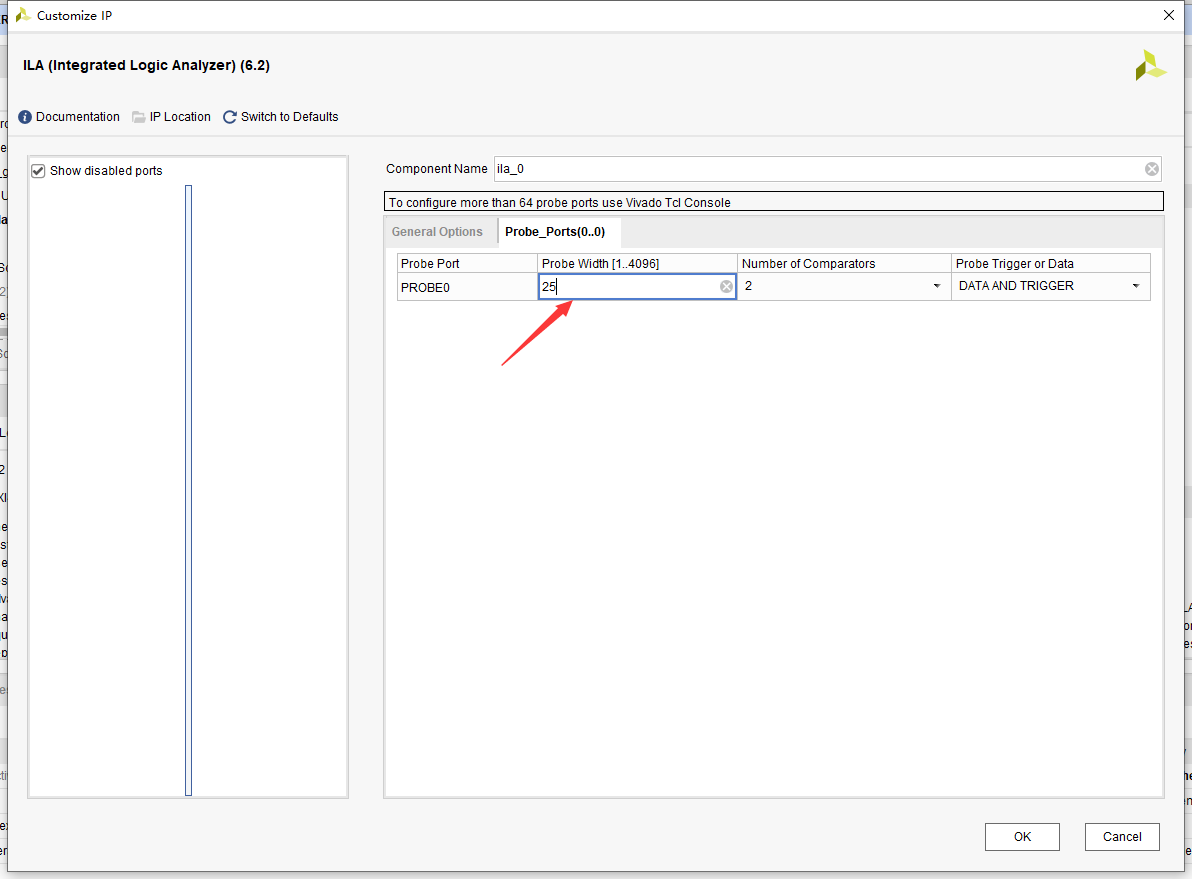

11 . Probe配置,我们需要采样大概十几个信号线信号,所以写入25个,然后点击OK,点击Generate生成IP输出文件。

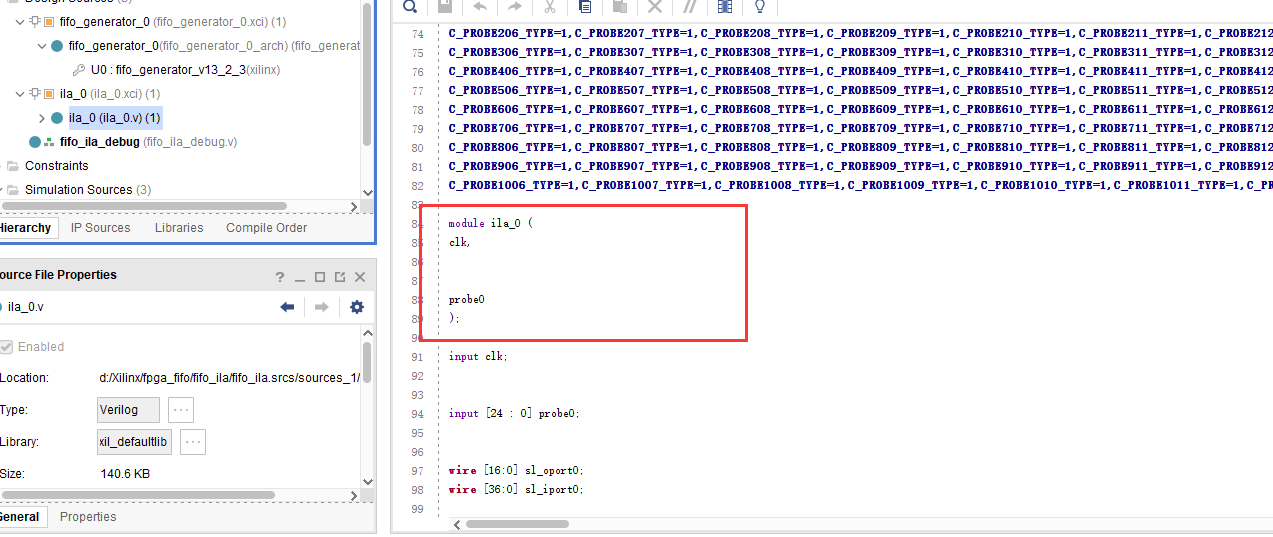

12 . Sources 窗口中的ila_0 IP就被添加进来了。点击ila_0 IP核左边箭头展开,等待展开完成,可以看到一 个顶层ila_0.v文件,打开即可看到模块接口信号。我们将它例化到fifo_ila_debug模块中。

13.代码

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: yu meng ya

//

// Create Date: 2022/04/30 16:38:46

// Design Name: FIFO读写ILA调试

// Module Name: fifo_ila_debug

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module fifo_ila_debug(

input wire clk,

input wire rstn

);

parameter STATE_IDLE='d0;

parameter STATE_WRITE='d1;

parameter STATE_READ='d2;

parameter CLK_FREQ=50000000;//input clk 50m

reg [31:0]counter_reg;

reg [3:0]system_state_reg;

reg [9:0]state_timeout_reg;

reg [7:0]write_data_reg;

wire[7:0] read_data;

wire [7:0]write_data;

reg read_en_reg;

reg write_en_reg;

wire is_write_read_flag;

wire fifo_full;

wire fifo_empty;

wire [24:0]ila_probe0;

wire read_en;

wire write_en;

wire [3:0]system_state;

assign read_en=read_en_reg;

assign write_en=write_en_reg;

assign system_state=system_state_reg;

assign write_data[7:0]=write_data_reg[7:0];

assign is_write_read_flag=(system_state[3:0]==STATE_IDLE)?'b0:'b1;

assign ila_probe0[0]=is_write_read_flag;

assign ila_probe0[1]=write_en;

assign ila_probe0[2]=read_en;

assign ila_probe0[3]=fifo_full;

assign ila_probe0[4]=fifo_empty;

assign ila_probe0[12:5]=write_data[7:0];

assign ila_probe0[20:13]=read_data[7:0];

assign ila_probe0[24:21]=system_state[3:0];

//always block ,1s triger onece to read write

always@(posedge clk or negedge rstn)begin

if(rstn=='b0)begin

counter_reg<='b0;

end

else begin

if(counter_reg<(CLK_FREQ-'b1))counter_reg<=counter_reg+'b1;

else counter_reg<='b0;

end

end

//state machine

always@(posedge clk or negedge rstn)begin

if(rstn=='b0)begin

system_state_reg<='b0;

state_timeout_reg<='b0;

end

else begin

if(counter_reg==(CLK_FREQ-'b1))begin

system_state_reg<=STATE_WRITE;

state_timeout_reg<='b0;

end

else begin

if(system_state_reg==STATE_WRITE)begin//write fifo state

if(state_timeout_reg<'d256)state_timeout_reg<=state_timeout_reg+'b1;

else begin

state_timeout_reg<='b0;

system_state_reg<=STATE_READ;

end

end

else if(system_state_reg==STATE_READ)begin//read fifo state

if(state_timeout_reg<'d256)state_timeout_reg<=state_timeout_reg+'b1;

else begin

state_timeout_reg<='b0;

system_state_reg<=STATE_IDLE;

end

end

end

end

end

//write read logic generate

always@(posedge clk or negedge rstn)begin

if(rstn=='b0)begin

write_data_reg<='b0;

end

else begin

if(system_state_reg==STATE_WRITE)begin

write_data_reg<=write_data_reg+'b1;

read_en_reg='b0;

write_en_reg<='b1;

end

else if(system_state_reg==STATE_READ)begin

write_data_reg<='b0;

read_en_reg='b1;

write_en_reg='b0;

end

else if(system_state_reg==STATE_IDLE)begin

write_data_reg<='b0;

read_en_reg='b0;

write_en_reg='b0;

end

end

end

fifo_generator_0 fifo_generator_0_inst

(

.clk(clk),

.srst(~rstn),

.din(write_data),

.wr_en(write_en),

.rd_en(read_en),

.dout(read_data),

.full(fifo_full),

.empty(fifo_empty)

);

ila_0 ila_0_inst

(

.clk(clk),

.probe0(ila_probe0)

);

endmodule

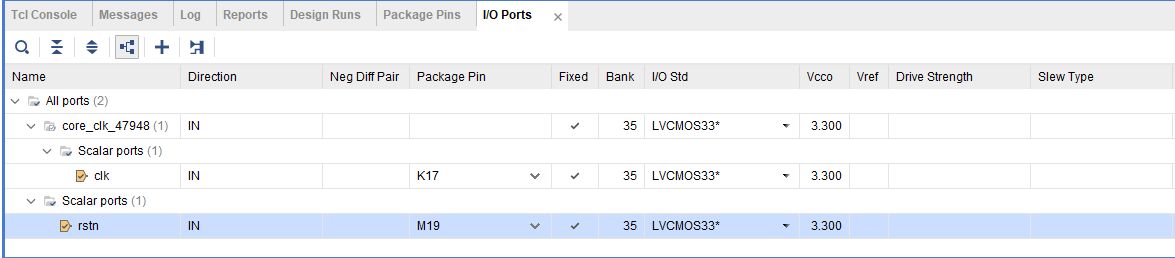

14.引脚绑定,点击open Elaborated Design

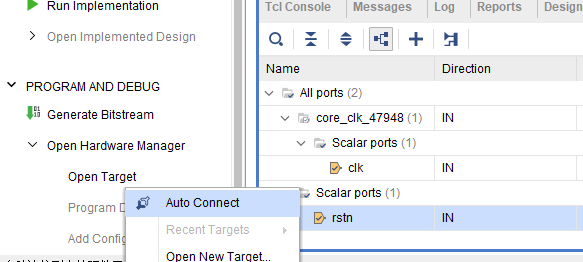

15.点击Auto Connect

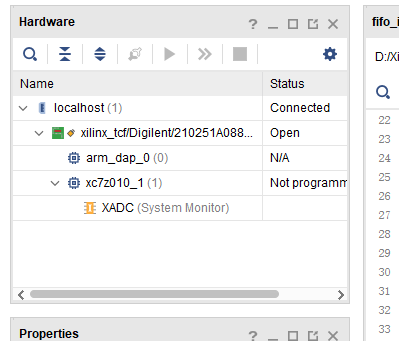

16.连接完成之后我们可以看到,Hardware下面找到了稳定芯片,已经连接上。

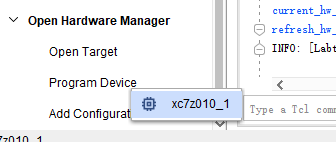

17.PROGRAM AND DEBUG下面的Program Device可以用了。我们点击Program Device,弹出右边的xc7010_1,点击它进行下载

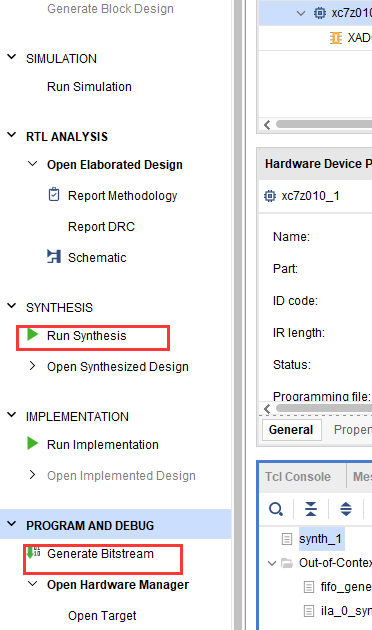

18.点击Run synthesis进行综合,然后点击Generate Bitstream

19.我们点击Program Device,弹出右边的xc7010_1,点击它进行下载

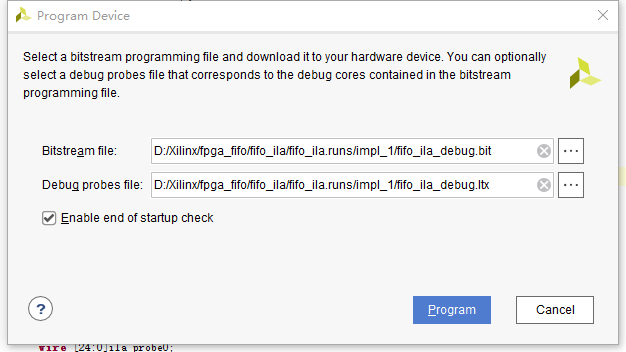

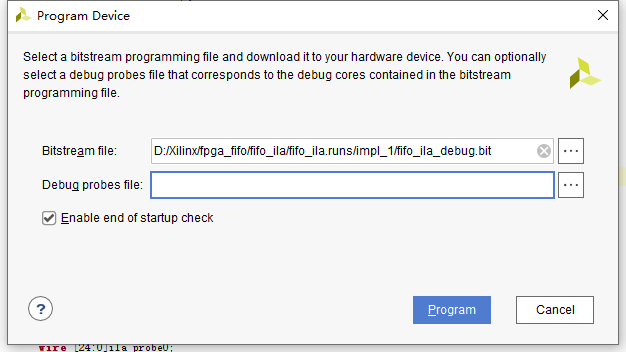

然后,弹出对话框我们可以看到其实下载包含了两个文件。第一个文件是我们的比特文 件。第二个文件是我们的dug文件,由于调用了ILA模块,系统自动生成一个debug文件,如 果debug结束,不需要在线调试,将ILA模块删掉,这个下载对话框去掉debug文件,不用即可。我们点击program进行下载。

20.点击program

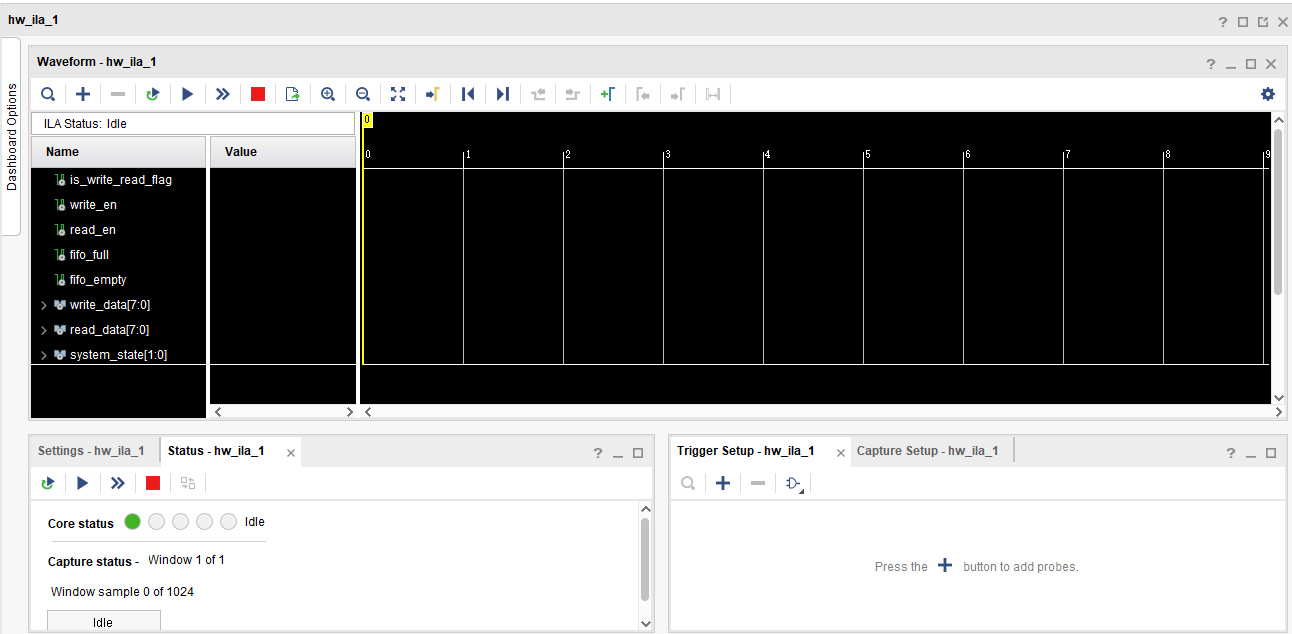

21.下载完成后就会弹出一个在线调试界面

22.接下来我们要对这些信号进行抓取。首先,信号抓取,需要一个触发条件。触发条件可以是某个状态,比如根信号是0还是1,即可马上开始触发采样,也可以是一个电平跳变,上升沿、下降沿等。我们分析代码可以知道,每隔一秒,状态机触发一次读写操作。我们有个信号,is_write_read_flag。这个逻辑当状态机处于读写操作时为1,而这个信号从0变成1的上升沿即代表开始写状态,写完256个时钟周期变为读状态,一共维持了512个周期。而我们ILA采样深度为1024,完全足够抓取到整个操作。首先我们来设置触发条件,点击Dashboard options 打开左边隐藏界面。

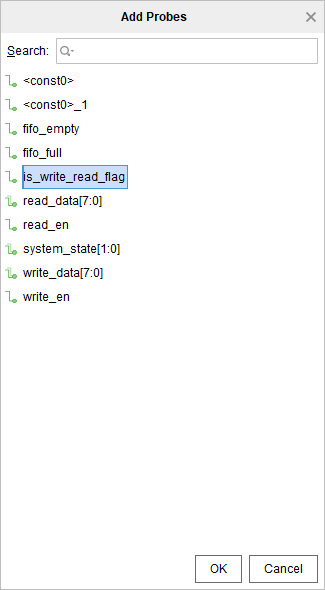

23. 然后,我们点击中间的+号添加触发信号

24.选择is_write_read_flag,点击OK

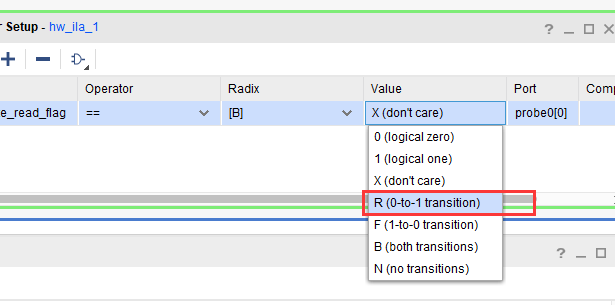

25.我们将value栏下拉,可以看到很多触发条件。我们选则R(0- to-1transition)这一项,代表这个信号上升沿跳变触发采样。

26. Settings窗口保持默认,triger position inwindow是指采样出来的触发 条件发生时刻在窗口的位置,我们默在中间,512,方便查看波形。Refresh rate默认500,指 的是波形刷新率。

27.点击图标,已经抓取到了波形