译码器

yummy

阅读:1672

2022-03-31 22:39:19

评论:0

译码是编码的逆过程,在编码时,每一种二进制代码都赋予了特定含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

译码器是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。

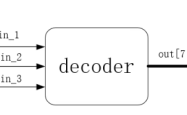

实验目标:实现38译码器,按键和LED的结合

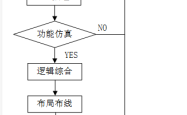

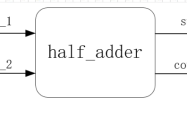

实验框图

真值表

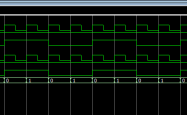

波形图

代码实现

// Filename﹕ decoder.v

// Author﹕YMY

// Description﹕译码器模块

// Calledby﹕/

// RevisionHistory﹕22-03-31

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

module decoder(

input wire in_1 ,//输入信号1

input wire in_2 ,//输入信号2

input wire in_3 ,//输入信号

output reg [7:0] out_data //输出数据

);

//根据真值表输入输出

always @(*) begin

case ({in_1,in_2,in_3})

3'b000 : out_data = 8'b0000_0001 ;

3'b001 : out_data = 8'b0000_0010 ;

3'b010 : out_data = 8'b0000_0100 ;

3'b011 : out_data = 8'b0000_1000 ;

3'b100 : out_data = 8'b0001_0000 ;

3'b101 : out_data = 8'b0010_0000 ;

3'b110 : out_data = 8'b0100_0000 ;

3'b111 : out_data = 8'b1000_0000 ;

default: out_data = 8'b0000_0001 ;

endcase

end

endmodule

仿真测试代码

// Filename﹕ tb_decoder.v

// Author﹕YMY

// Description﹕译码器测试模块

// Calledby﹕/

// RevisionHistory﹕22-03-31

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

module tb_decoder();

reg in_1 ;

reg in_2 ;

reg in_3 ;

wire out_data ;

//产生随机数,%2 产生的非随机数为0或者1,10ns产生一次

always#10 in_1 = {$random}%2;

always#10 in_2 = {$random}%2;

always#10 in_3 = {$random}%2;

initial begin

//设置时间格式的系统函数

$timeformat(-9,0,"ns",6);//-9 10^-9表示ns ,0 表示小数位数,6表示打印的最下数字字符是6个

//检测打印函数

$monitor("@time = %b in_1 =%b in_2 =%b in_3 =%b out_data =%b",$time,in_1,in_2,in_3,out_data);//%b二进制数

end

decoder decoder_inst

(

.in_1 (in_1 ),//输入信号1

.in_2 (in_2 ),//输入信号2

.in_3 (in_3 ),//输入信号

.out_data (out_data) //输出数据

);

endmodule

仿真测试

本文 zblog模板 原创,转载保留链接!网址:http://xn--zqqs03dbu6a.cn/?id=15

声明

1.本站遵循行业规范,任何转载的稿件都会明确标注作者和来源;2.本站的原创文章,请转载时务必注明文章作者和来源,不尊重原创的行为我们将追究责任;3.作者投稿可能会经我们编辑修改或补充。