FPGA时序分析和时序约束

时序分析:目的是通过分析FPGA设计中哥寄存器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟之间的关系。

数据和时钟传输路径是由EDA软件,通过针对特定器件布局布线得到的

时序约束

告知EDA软件,该设计需要达到怎样的时序指标,然后EDA软件会根据时序约束的各个参数,尽力优化布局布线,以达到该约束的指标。

协助EDA软件分析设计的时序路径,以产生相应的时序报告

时序分析的基本模型

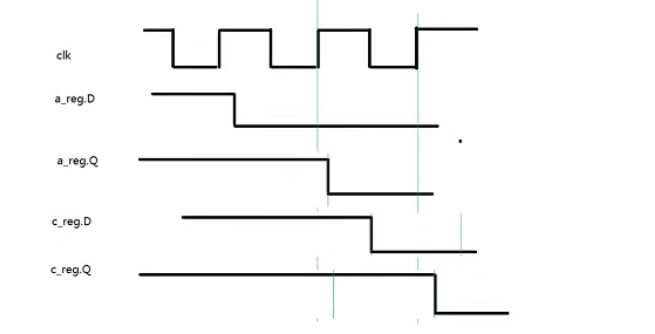

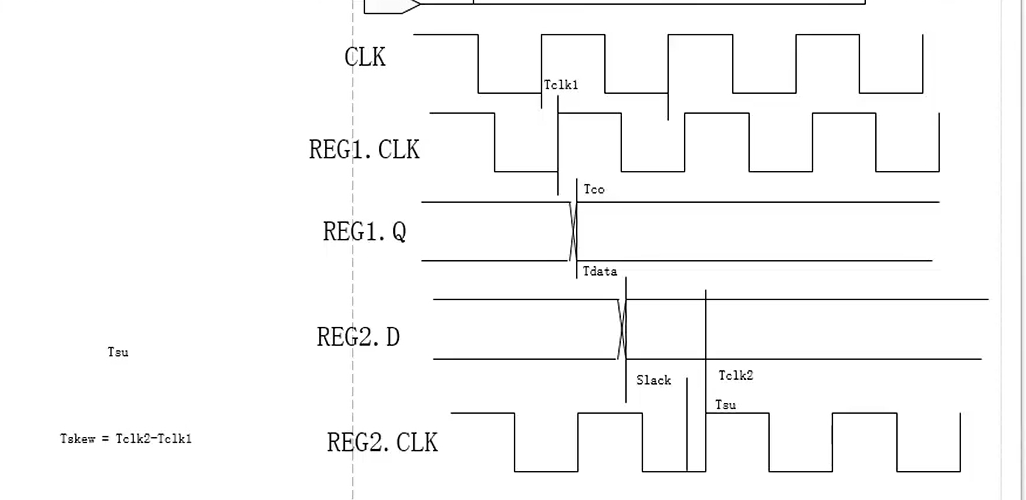

Tco(数据输出时间):时钟上升沿到达D触发器 到 数据输出Q端的延迟

Tsu(数据建立时间):D触发器D端口的数据必须比时钟上升沿提前Nns到达D触发器的端口

Tdata:从触发器Q出发到达目的寄存器D端口

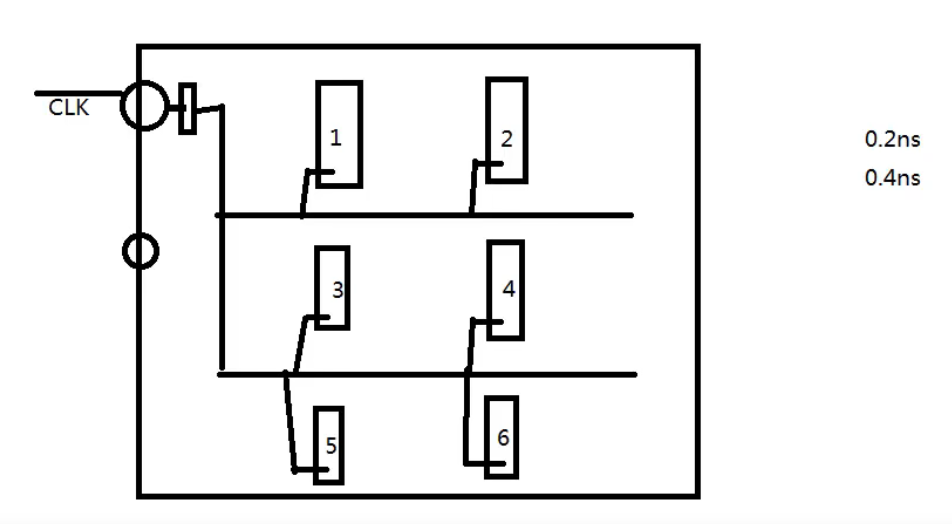

时钟树

尽量减小clk到达各个寄存器的时间差距

(SKew)时钟偏斜:时钟从端口出发,到达源寄存器和目的寄存器的时间差值

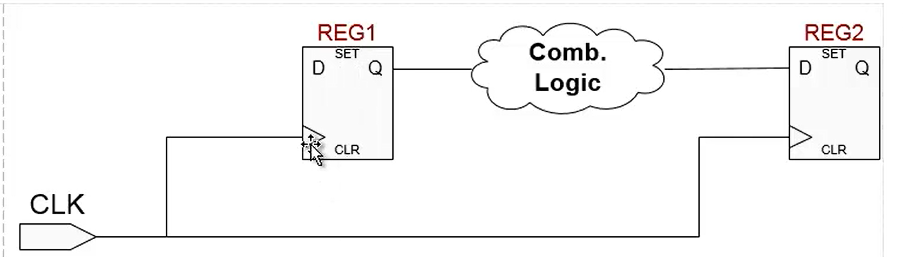

时序分析基本公式

Tclk1+Tco+Tdata<=Tclk+Tclk-Tsu

Slack=Tclk+Tskew-Tsu-Tco-Tdata

Slack(建立时间余量)>0,目的寄存器能够正确接收源寄存器发射过来的数据

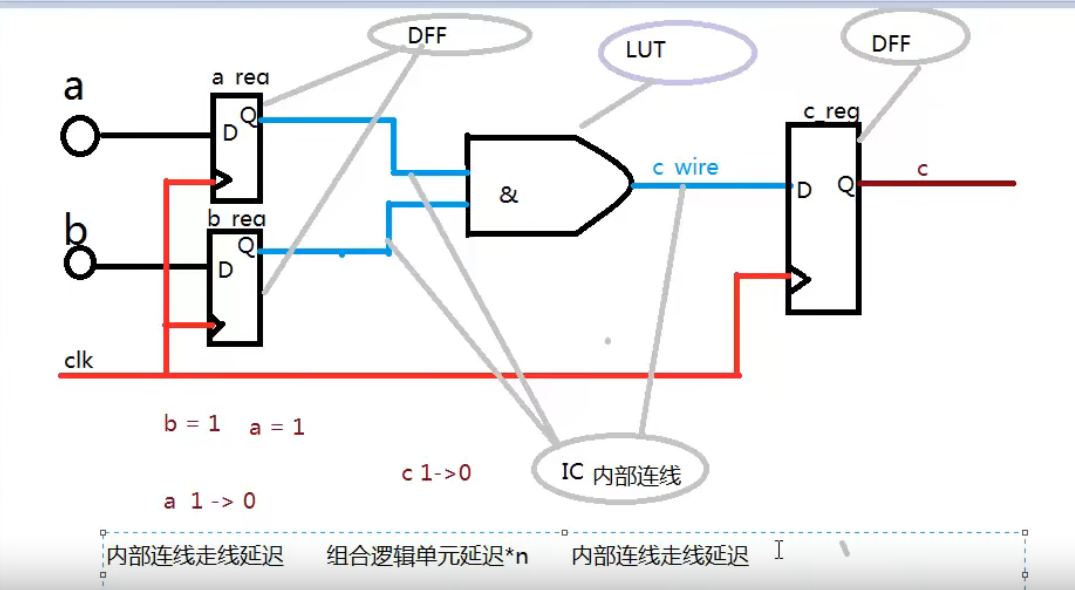

DFF=D触发器=寄存器

Tclk1:时钟信号从时钟源端口出发,到达源寄存器时钟端口的时间

Tco:时钟上升沿到达寄存器时钟端 到 数据输出到寄存器Q端的时间

Tdata:数据从源寄存器Q出发到达目的寄存器D端口的时间

Tclk:时钟周期

Tclk2:时钟信号从时钟源端口出发,到达目的寄存器时钟端口的时间

Tsu:寄存器要求的其数据端口的值必须提前于时钟上升沿达到其时钟端口的时间值

Tskew:时钟从源端口出发,到达目的寄存器和源寄存器时钟端口的时间差值(Tclk2-Tclk1)

Tclk1+Tco+Tdata:数据到达时间(TimeQuest)

Tclk+Tclk2-Tsu:数据需求时间

Slack:数据需求时间和数据到达时间的差值;如果为正值,目的寄存器能够正确接收源寄存器发射过来的数据;如果为负值,目的寄存器不能够正确接收源寄存器发射过来的数据。