分析实验工程

LED流水灯这个代码所描述的逻辑电路在Cyclone IV E在这个系列器件上能最高运行在多少频率的时钟?

这个需要时序分析来解决,通过TimeQuest进行分析

时序分析一定是基于某个逻辑设计在该特定器件上经过布局布线之后的网表(该网表包含了设计中每一个逻辑具体在该器件的什么资源上实现,而且还包括该资源在器件内的具体位置,还包括信号从每个节点传输到下一个节点的具体延迟时间)。时序分析不是对代码进行分析,而是在对真实的门级传输路径进行分析。

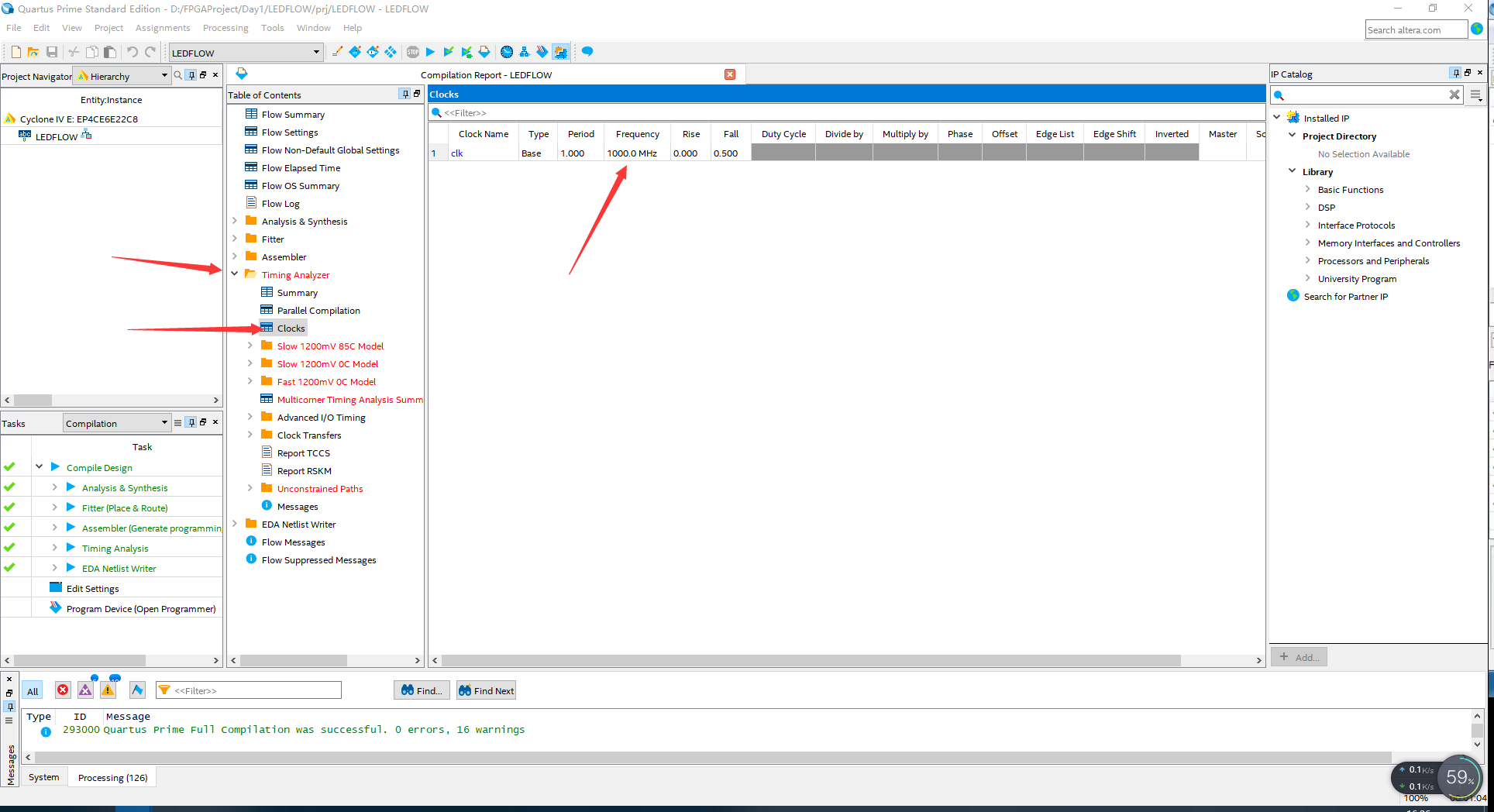

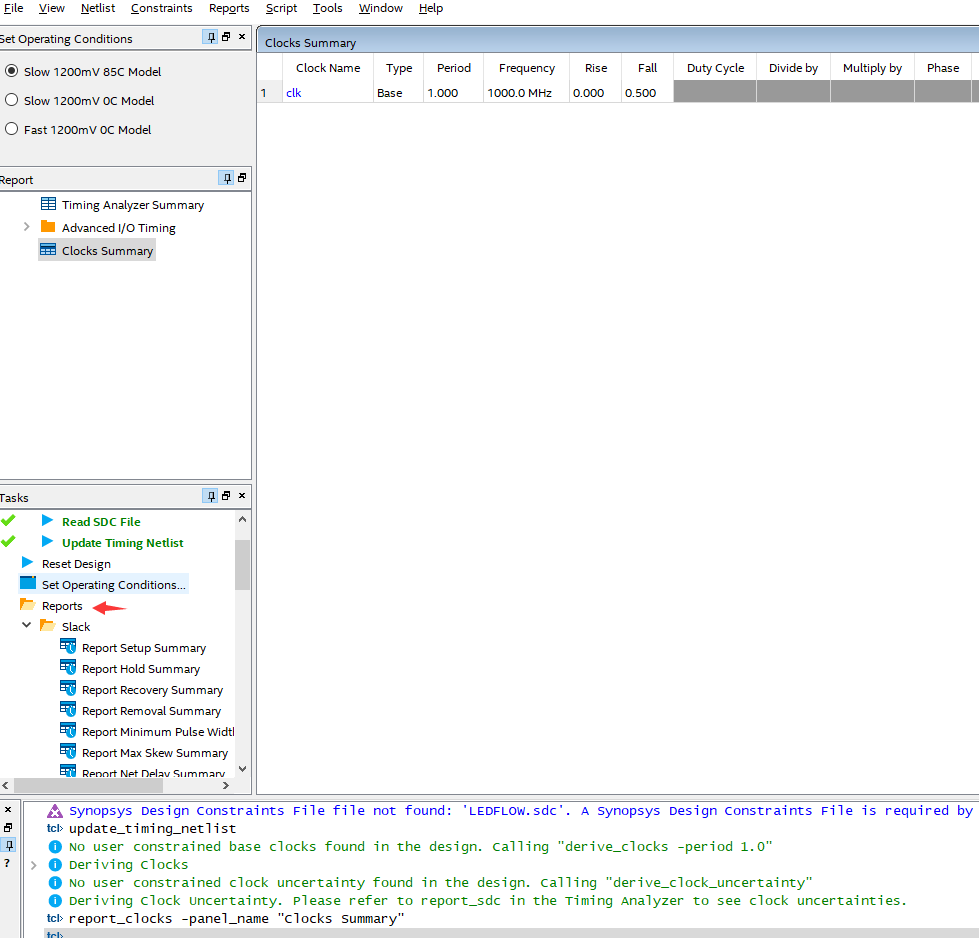

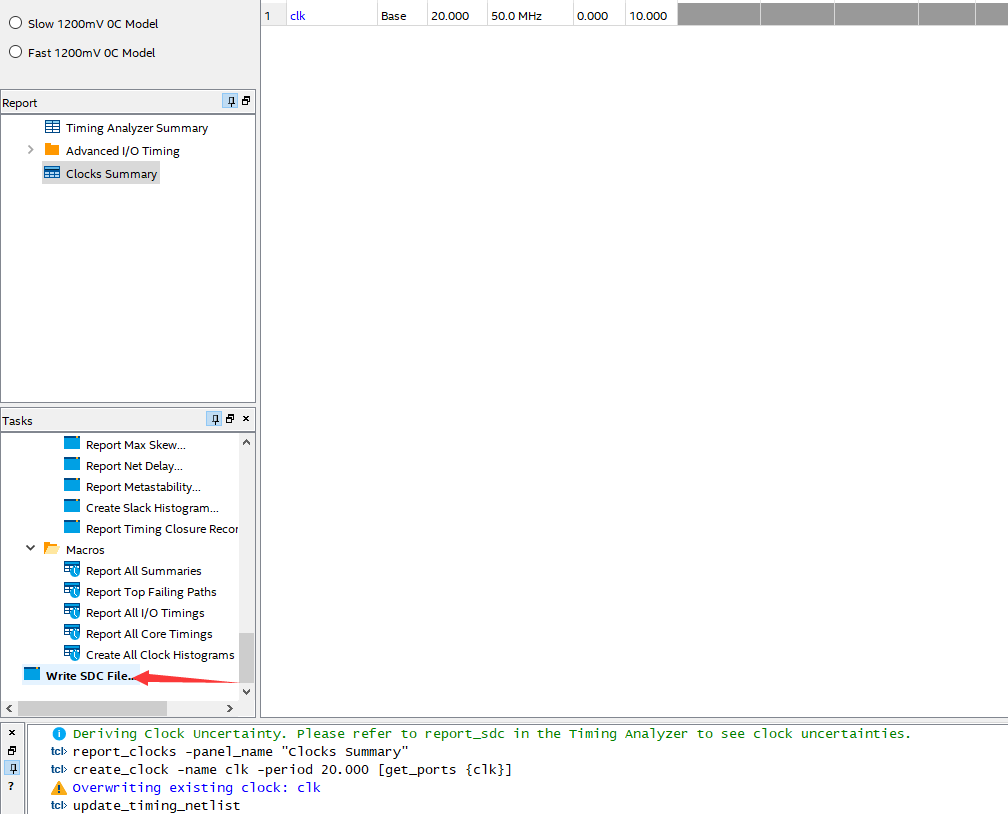

对代码进行全编译,点击Timing Analyzer-->Clocks

代码中设定的时钟频率为50MHZ,而时序分析中显示的是1GHZ。

Clocks:1Ghz(这个是软件报告的设计中的时钟约束频率)这是因为如果用户没有对时钟信号加约束,软件就会自动对分析出的时钟信号加入约束,这个约束会按照最大的可能来约束。

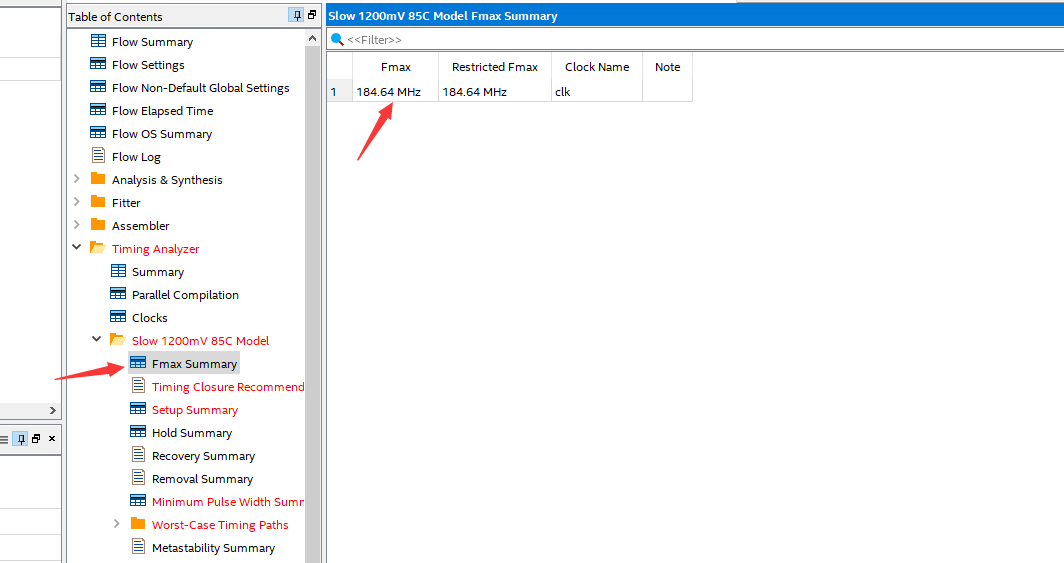

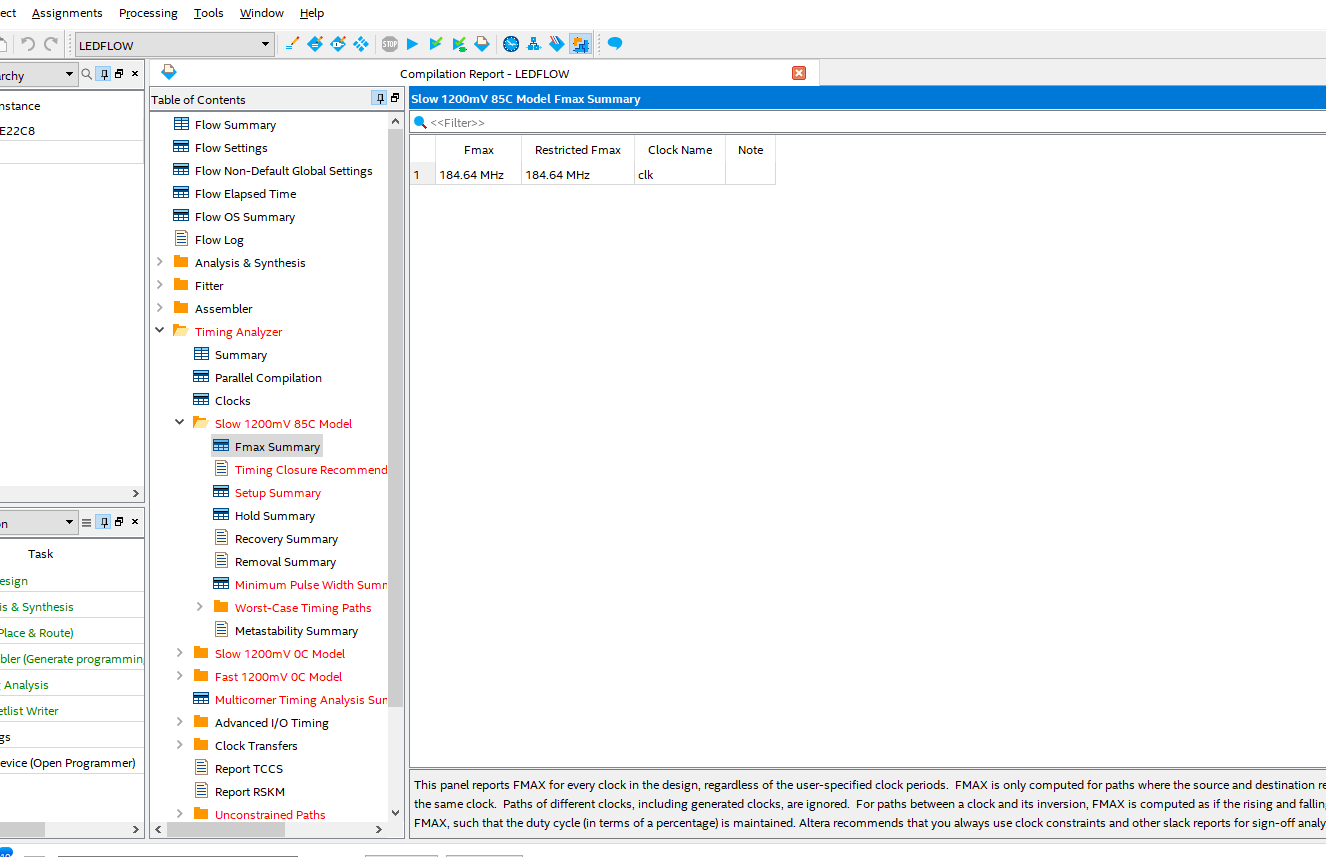

点击Fmax Summary查看最大时钟频率,184.64MHZ,该频率满足代码要求,但是不满足软件时序分析的要求

点击Setup:'clk',查看Slack,软件计算最高时钟频率的时候,是根据最坏路径的建立时间余量来计算的。

时序约束

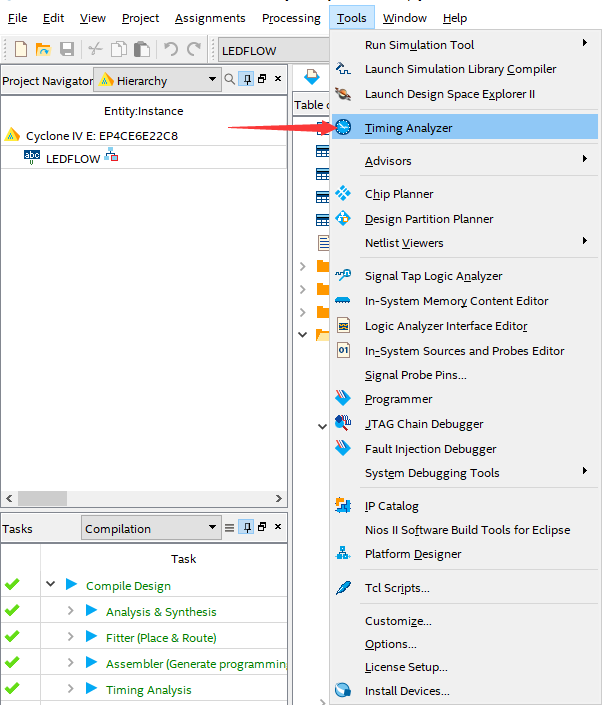

点击Tools-->Timing Analyzer

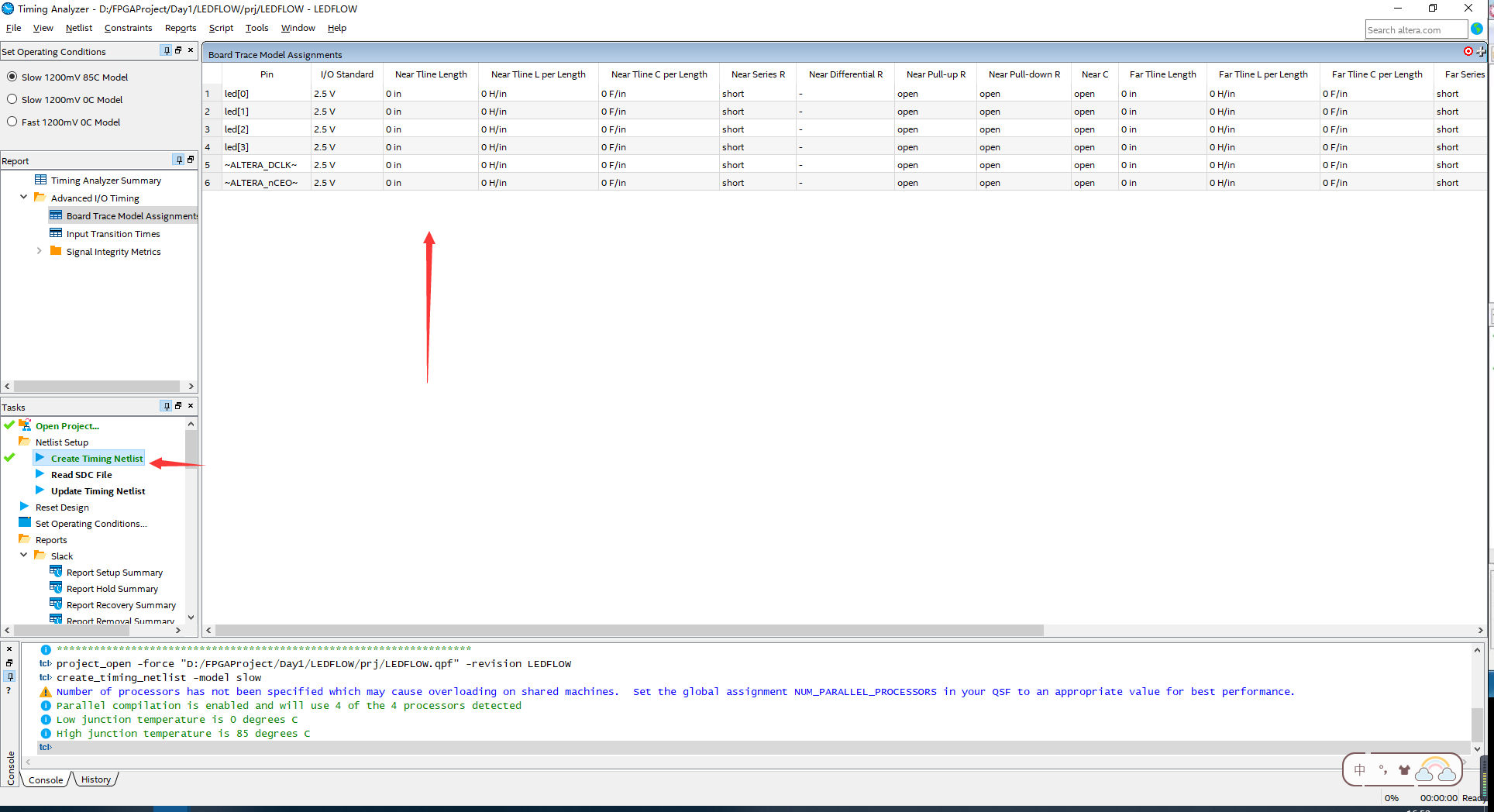

创建时序网表

点击Create Timing Netlist

读取SDC文件

查看报告

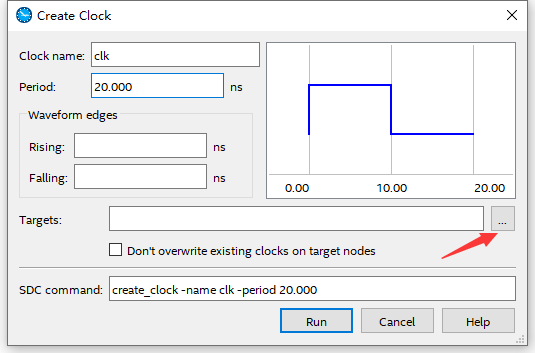

加入约束,点击Create Clocks

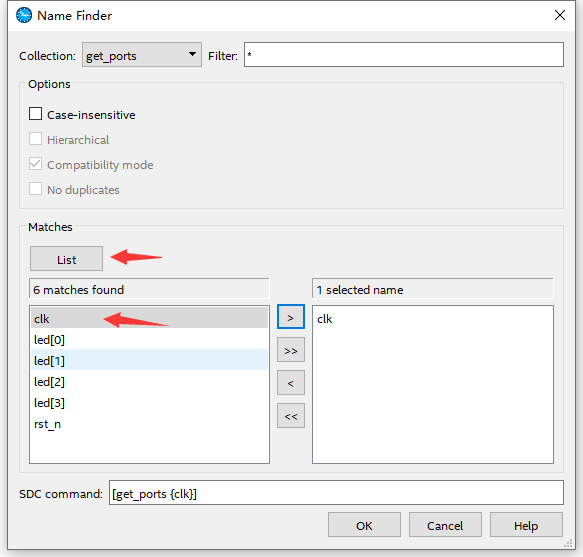

点击List,选择clk,点击ok,点击run

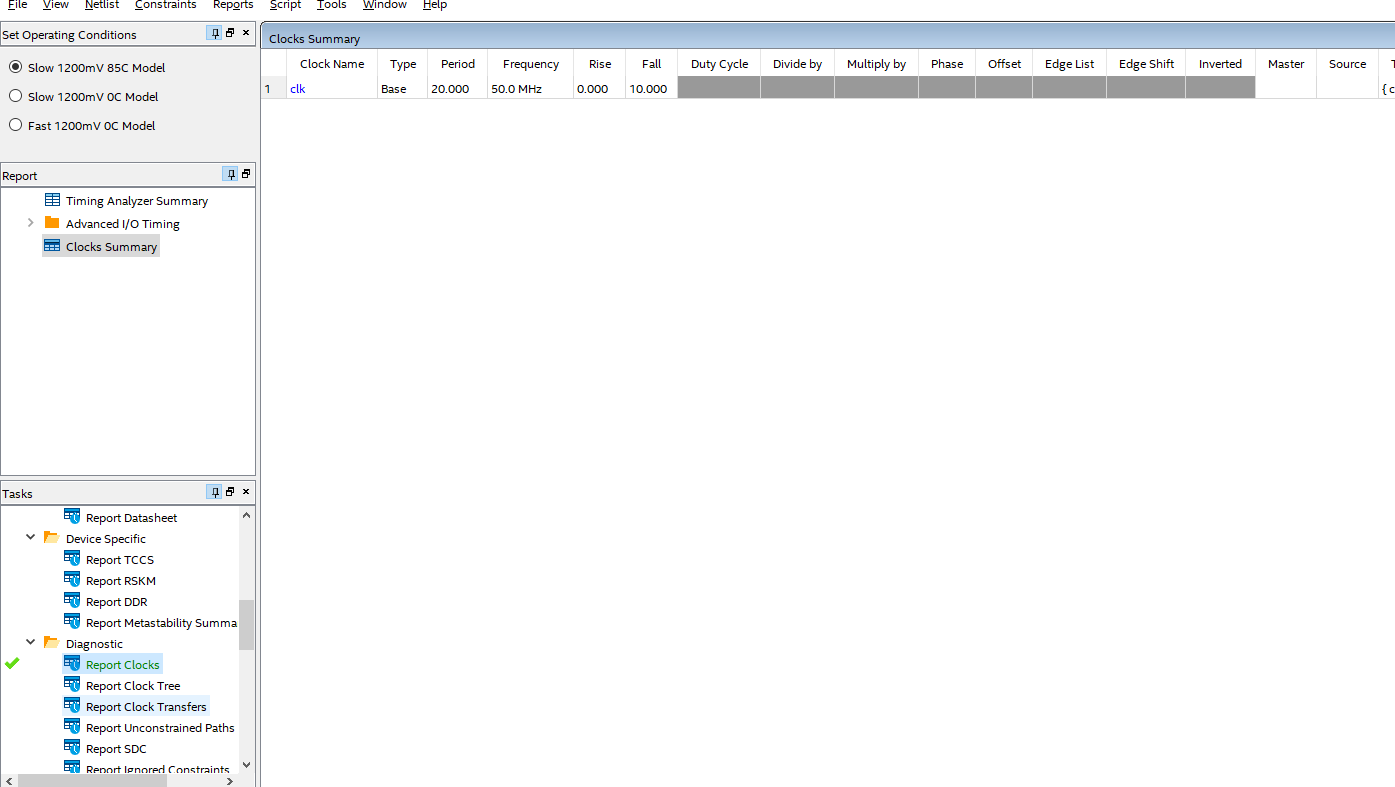

双击Report Clock,修改成功

约束的作用:1.指导EDA软件对设计的布局布线进行合理优化以尽量满足约束需求。2.给时序分析工具提供一个分析时序的参数

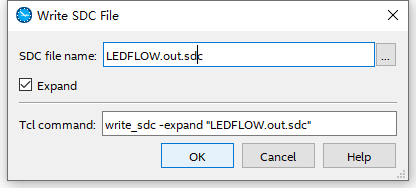

所有约束操作完成后,需要执行写SDC文件的操作,这个操作会生成包含所有约束的SDC文件

点击Write SDC File

点击ok

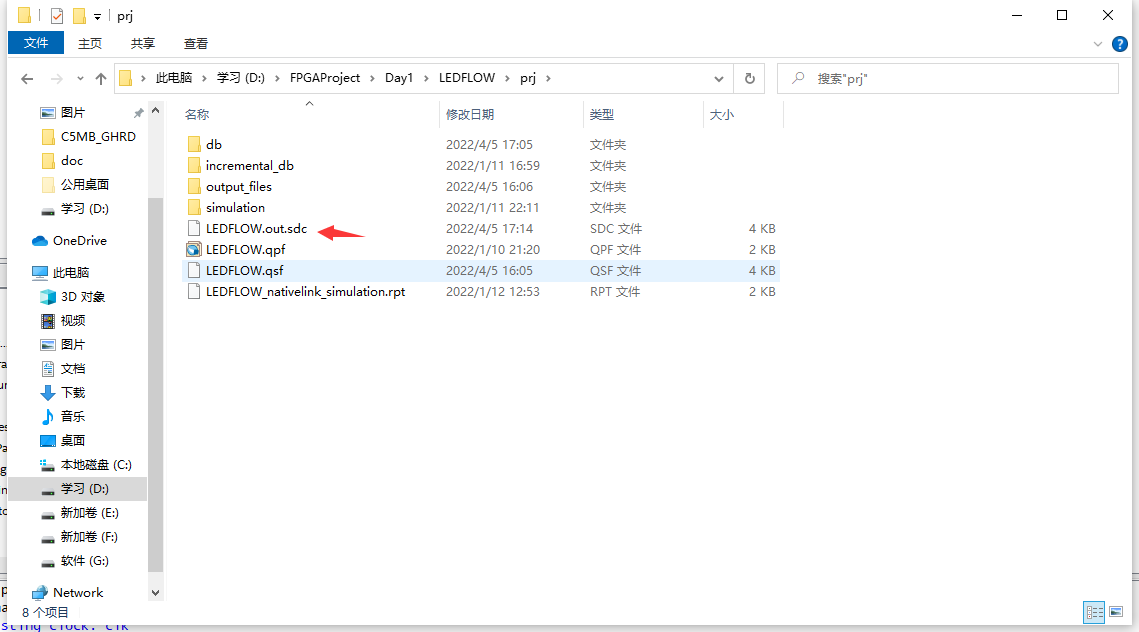

回到工程所在文件夹,就可以发现生成了SDC文件

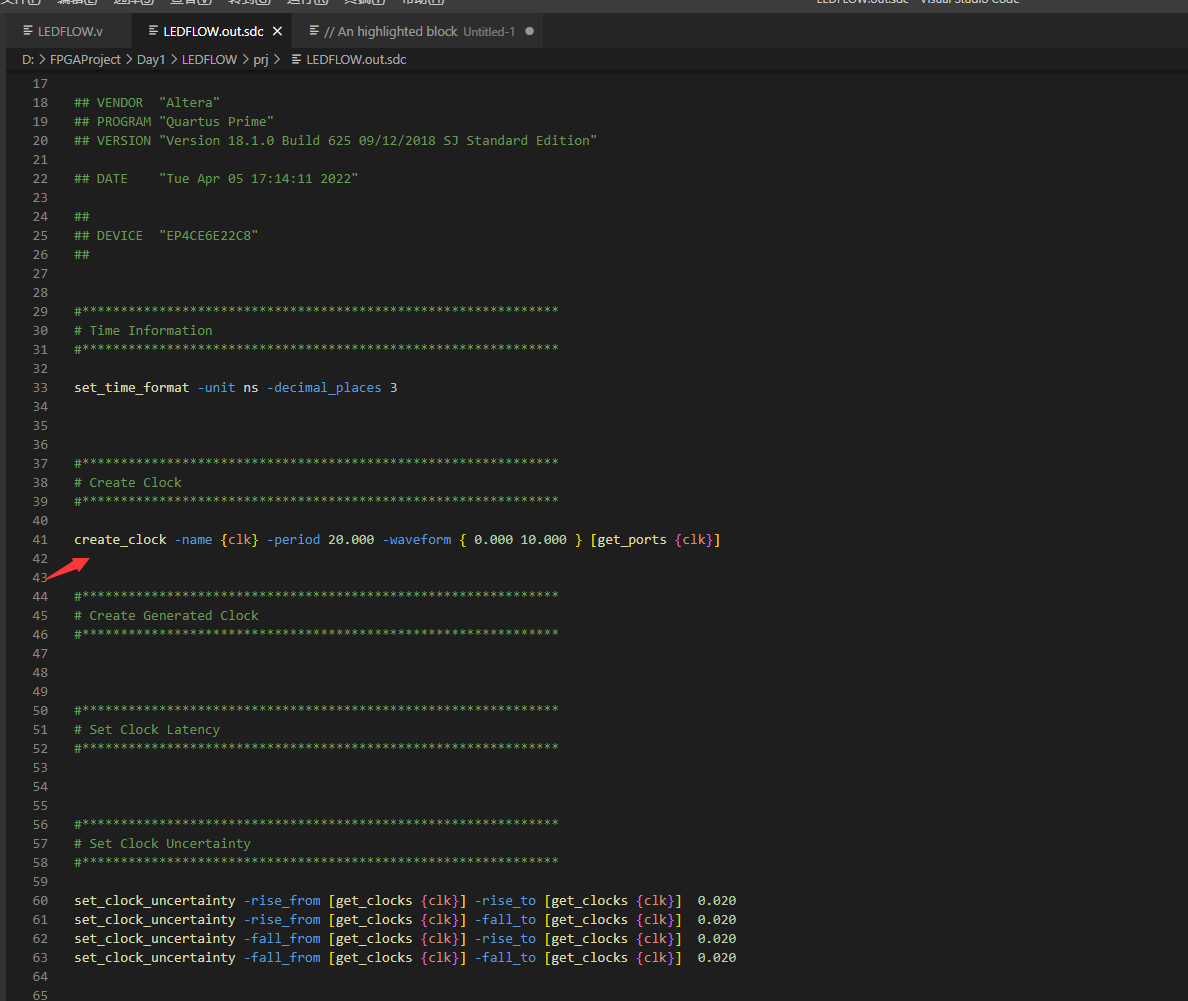

点击打开文件

重新编译工程,对设计进行布局布线

发现并没有什么改变,说明此代码是否约束,没有多大的意义。