基于Timequest软件来查看时序报告和分析时序路径

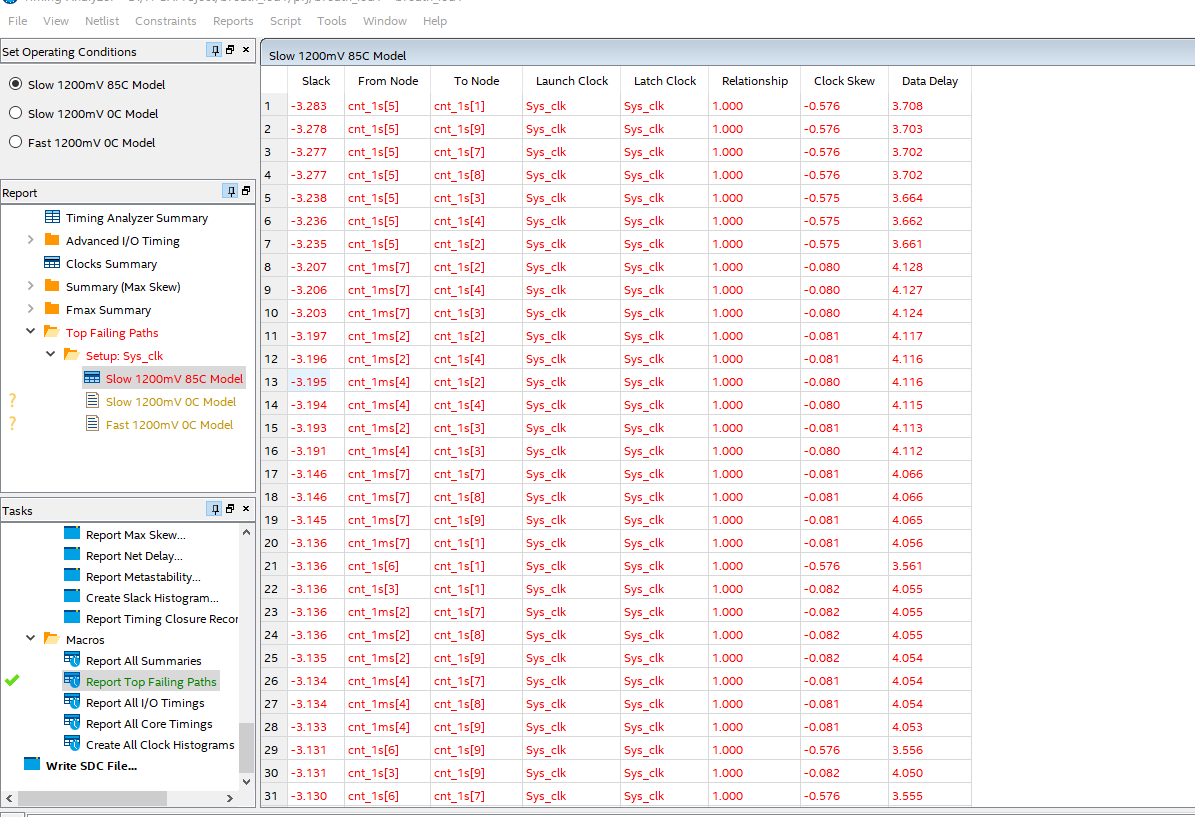

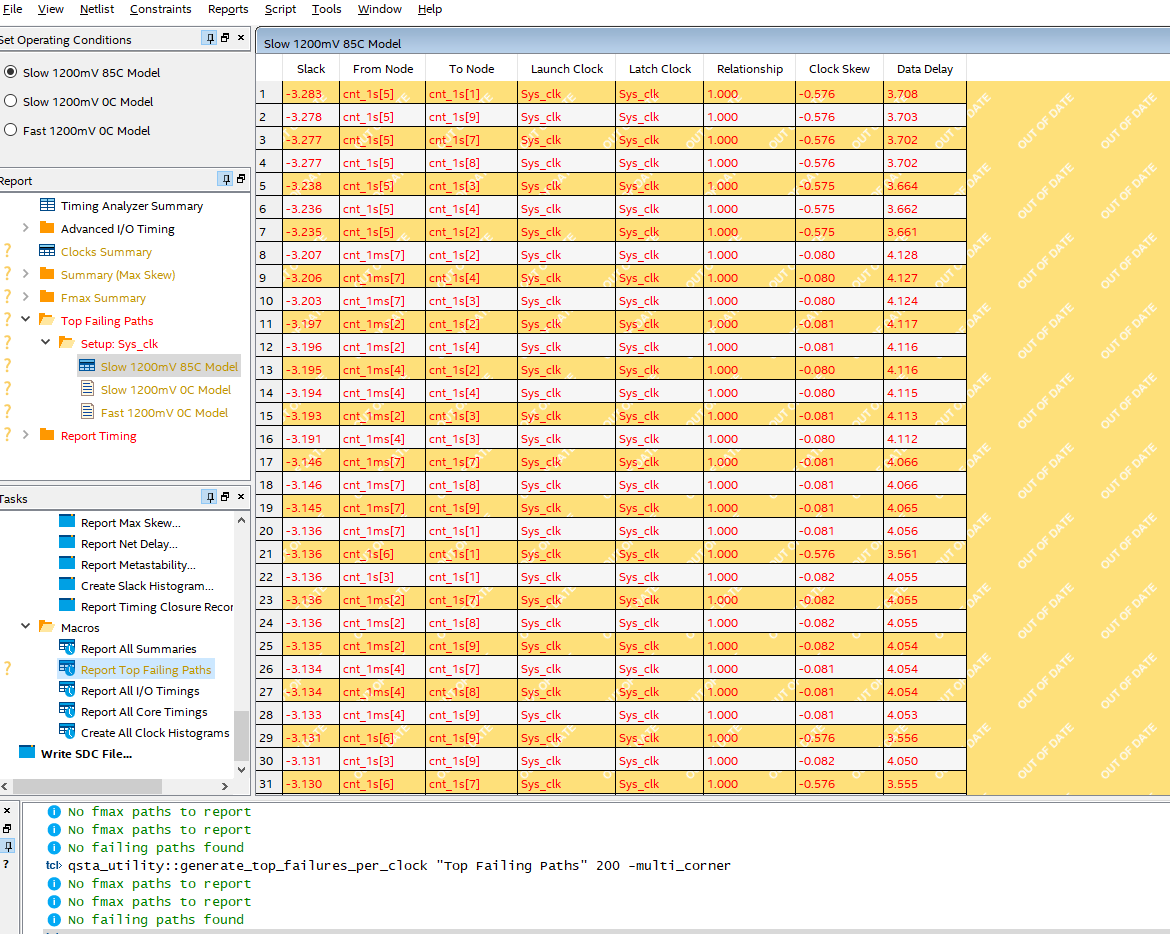

查看时序报告,报告时钟、报告时钟最大频率、查看关键路径余量 Report Top Failing Paths

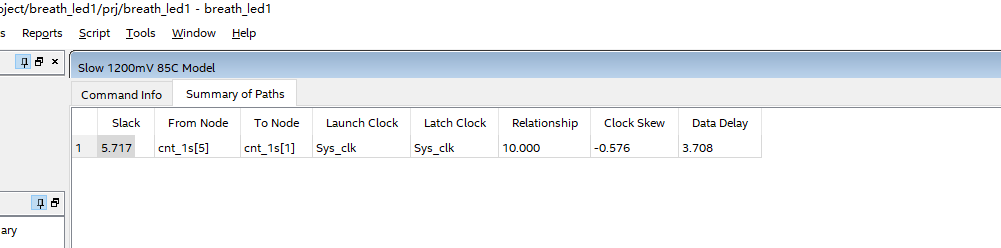

Slack 建立时间余量

From Node 起点、源寄存器

To Node 终点,目的寄存器

Launch Clock 源寄存器发射数据的时钟

Latch Clock 目的寄存器接收数据的时钟

Relationship Launch Clock edge 和 Latch Clock edge的时间差(如果两个时钟非同一个信号,而是有一定相位关系的同源时钟,则Relationship不再是时钟的周期值)

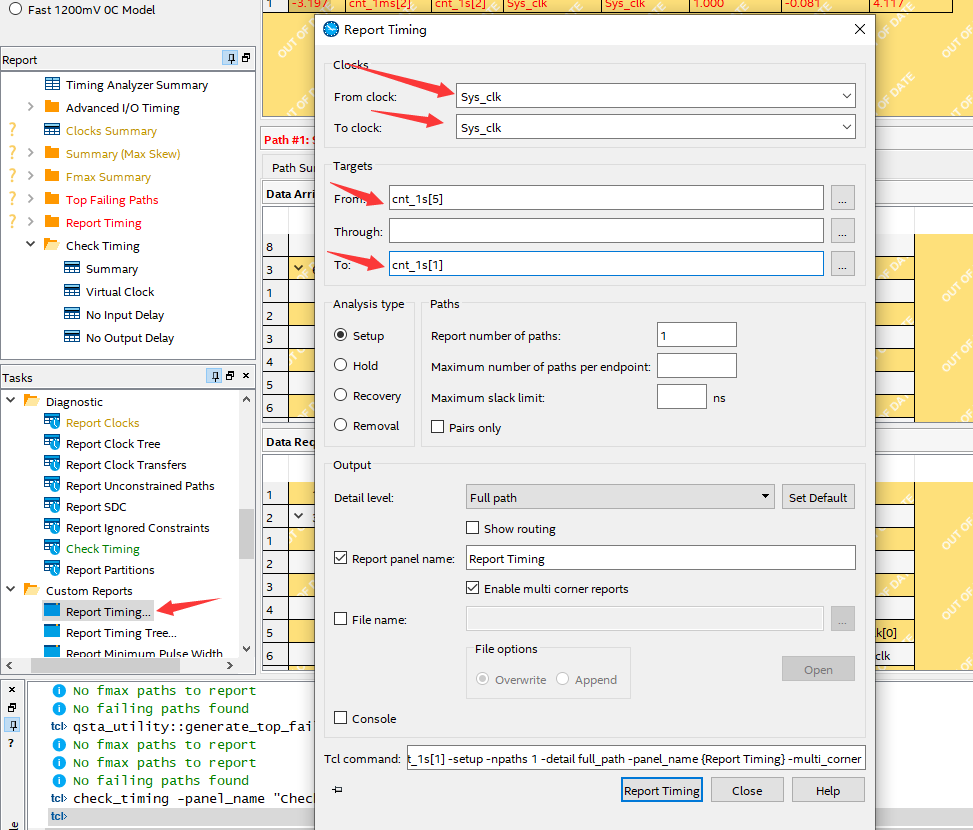

使用TimeQuest查看具体路径信息

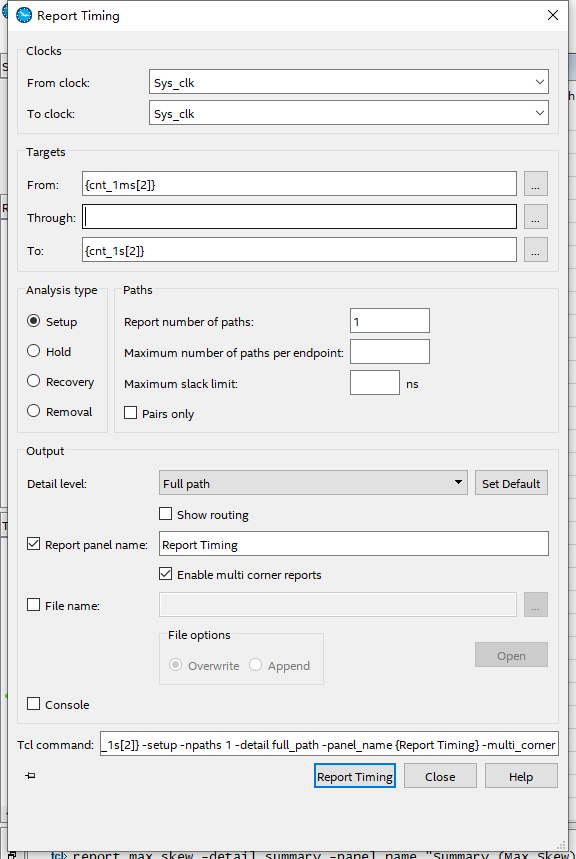

点击Report Timing

图中两条线段之间的路径太长,显示的不合理,需要改正

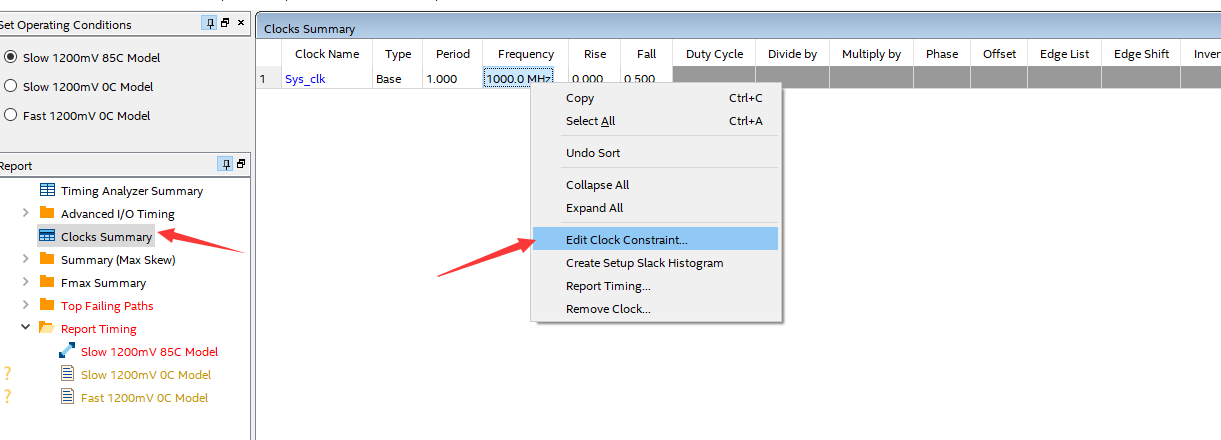

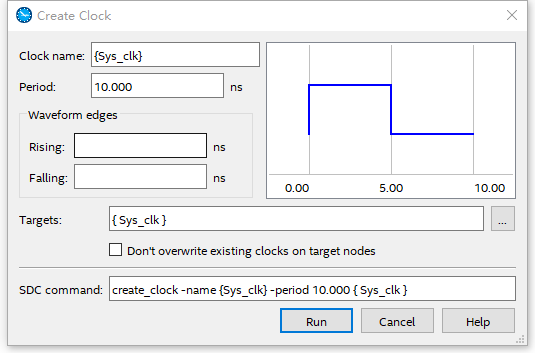

点击Clock Summary-->右击Edit Clock Constraint

周期改为10ns,点击run

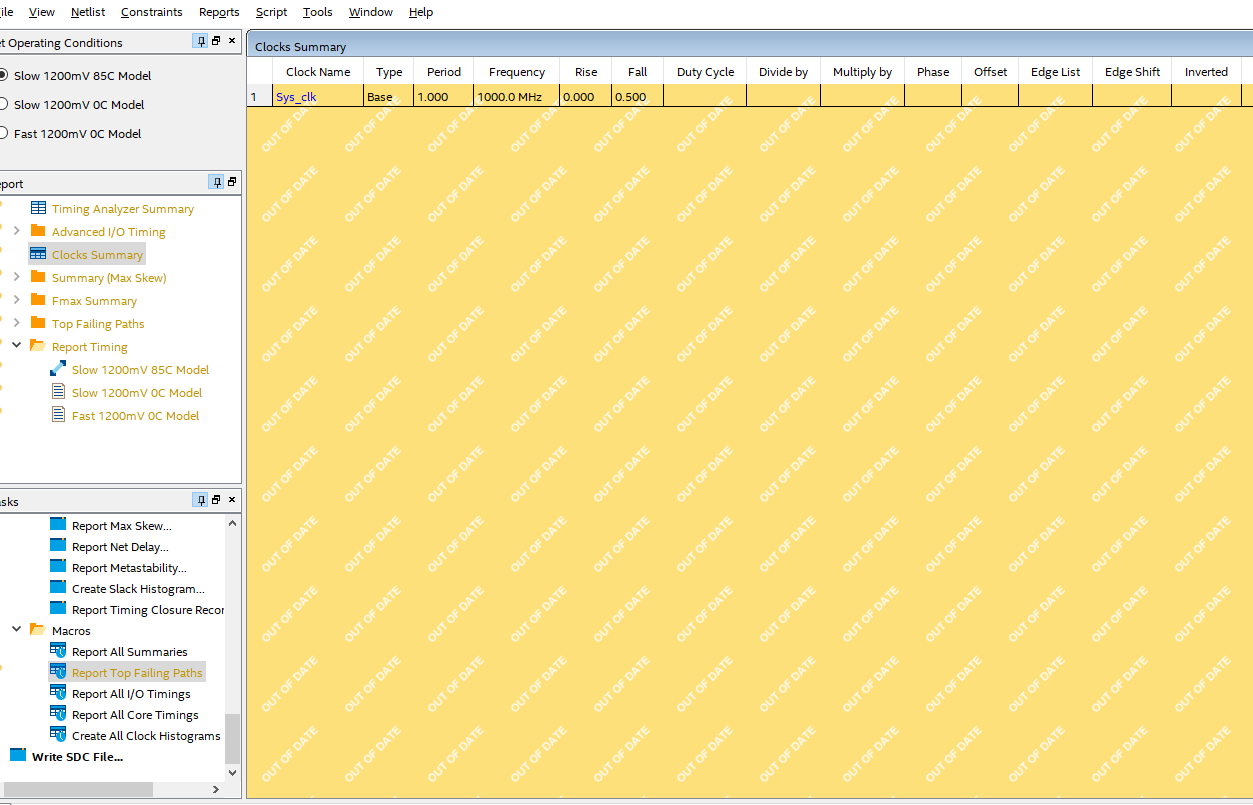

信号都失效了,需要重新报告

双击Report Top Failing Paths

手动报告路径

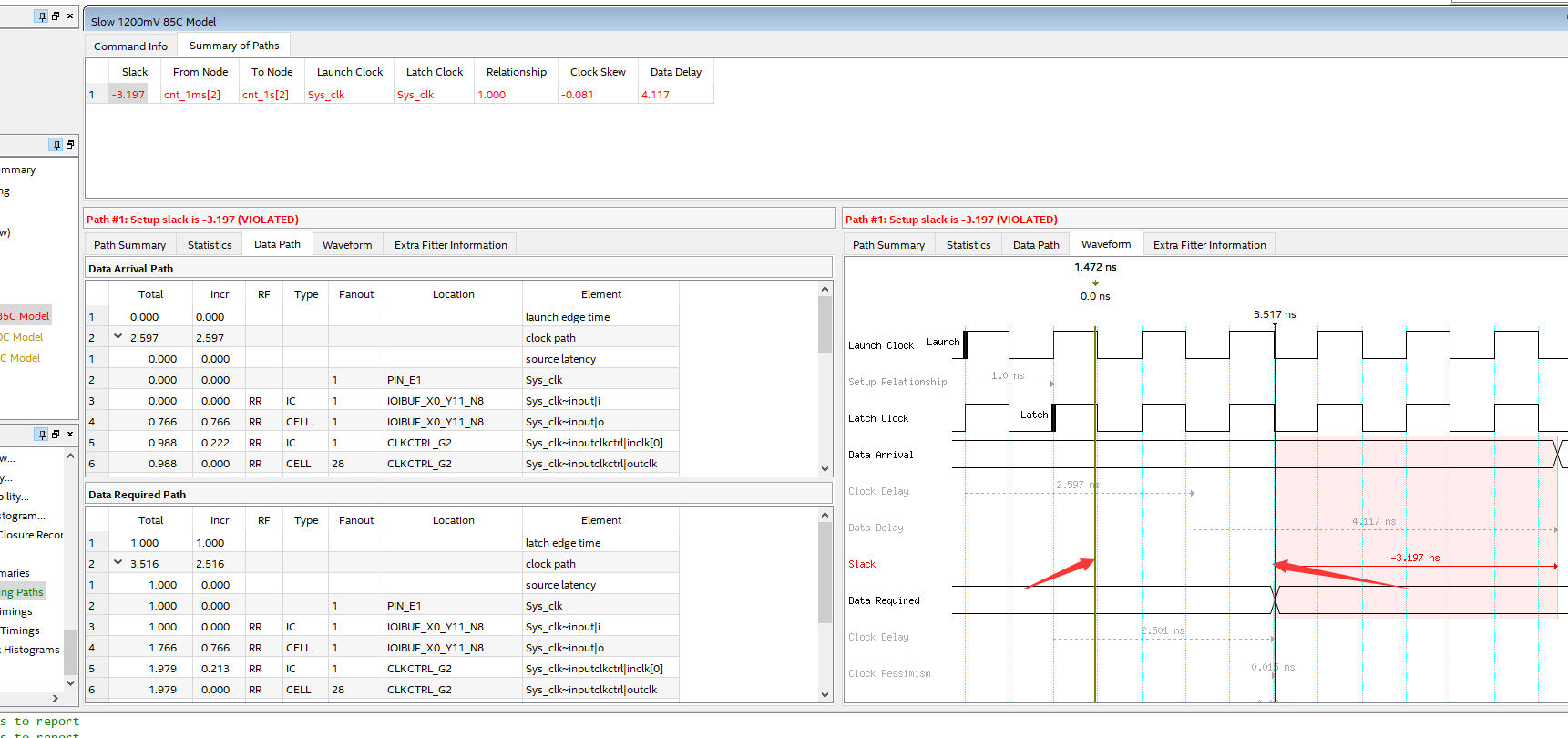

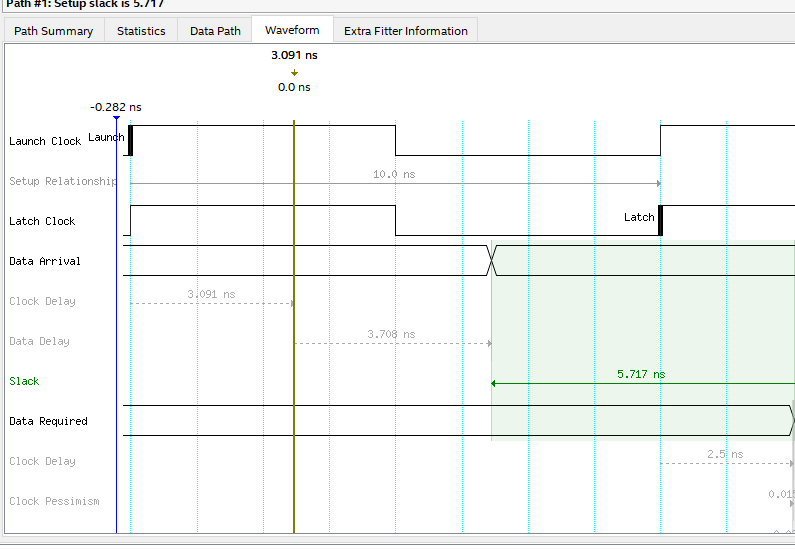

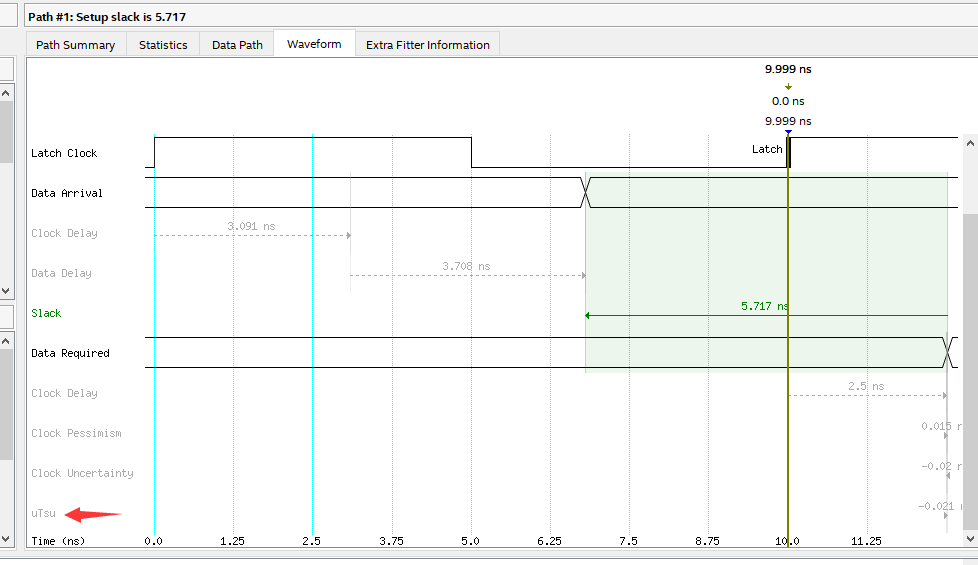

Tclk1=3.091,Tclk2=2.5ns,在Timing Analyzer中,将Tco和数据传输路径延迟Tdata合并称为data_delay,数据经过Tclk1和data_delay之后,到达目的寄存器的D端口

uTsu=-0.021ns

Tsu为负值是合理的,或者说,是Altera Cyclone IV E 这个系列的FPGA的寄存器时序模型的一个等效值

Tskew = -0.576ns

Tskew = Tclk2-Tclk1+0.015= -0.576ns;

Clock Pessimism = 0.015ns

时钟悲观值该值会被计算入Tskew

Clock Uncertainty = -0.02ns

时钟不确定,该值会被计算入data require time

Tclk2>=2.5ns,(分析计算Tclk2的时候,会认为时钟从源端口出发按照最快的速度达到目的寄存器时钟端口)

Tclk1<=3.091ns,(分析计算Tclk1的时候,会认为时钟从源端口出发按照最慢的速度达到目的寄存器时钟端口)

最终的目的是要分析Slack最小的路径,需要Tclk2的值按照最小情况算,需要Tclk1的值按照最大情况算.

引出一个矛盾:时钟在传输过程中,到达目的寄存器和源寄存器时,中间(开头)有一段路径是重合的

时钟通过同一段路径按照不同的速率计算出的时间在真实情况下是不存在的,我们在分析时钟的时候过分悲观,导致Skew值偏小,所以需要将这一段路径过分悲观的值补偿回来,加上一个时钟悲观值。

数据到达时间:Tclk1+Tco+Tdata

数据需求时间:Tclk+Tclk2-Tsu

Tskew= Tclk2-Tclk1+TClock Pessimism

Slack=Tclk+Tskew-Tsu-Tco-Tdata=Tclk+Tclk2-Tclk1+TClock Pessimism+TClock Uncertainty-Tsu-Tclk1-Tco-Tdata