IP核是什么

IP(Intellectual Property)知识产权,在半导体产业将IP核定义为“用于ASIC或FPGA中预先设计好的电路功能模块”。简言之,IP核即电路功能模块。

在数字电路中,将常用的且比较复杂的功能模块设计成参数可修改的模块,让其他用户可以直接调用这些模块。

IP核的存在形式

分类依据:产品交付方式

HDL语言形式--软核

硬件描述语言:可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少。

网表形式--固核

完成了综合功能块,可预布线特定信号或分配特定的布线资源

版图形式--硬核

硬核是完成提供设计的最终阶段产品--掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核的保护。

IP核的缺点

IP核往往不能跨平台使用

IP核不透明,看不到内部核心代码

定制IP需额外收费

PLL IP核简介

PLL(Phase Locked Loop)锁相环,是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

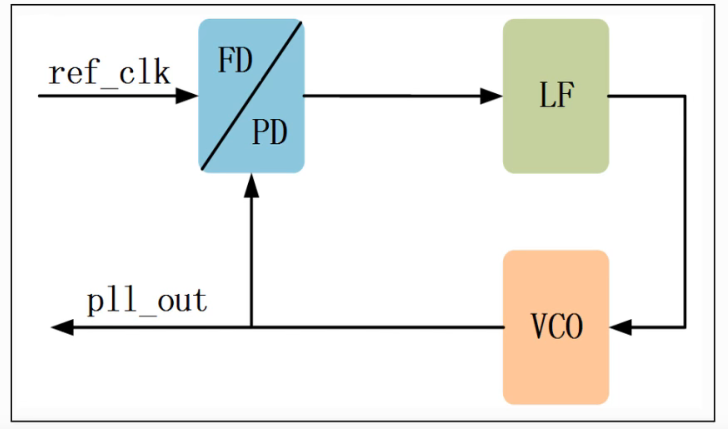

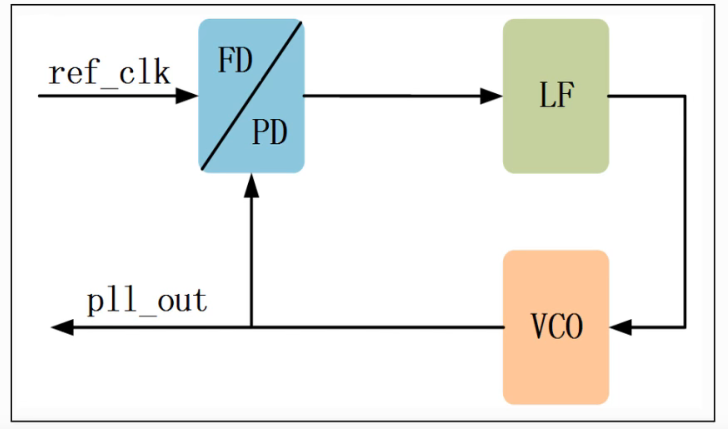

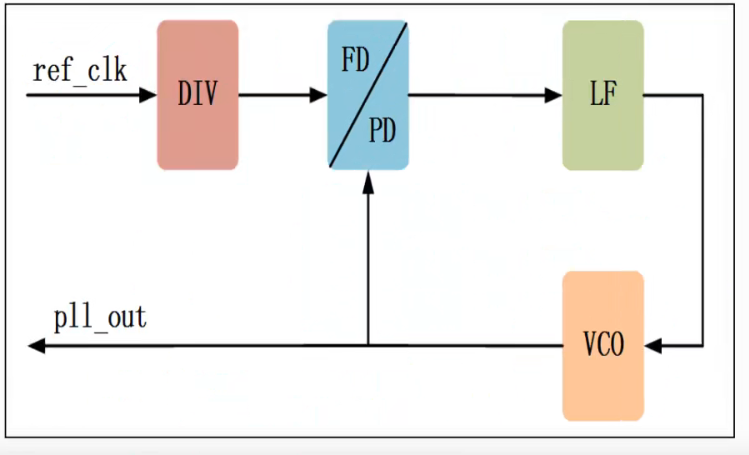

PLL的基本工作原理

FD/PD 鉴频鉴相器 LF 环路滤波器 VCO压控振荡器--输入电压越高,输出频率越高

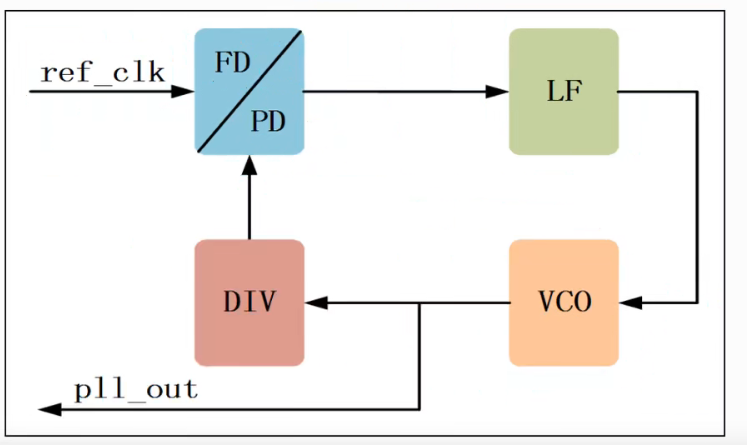

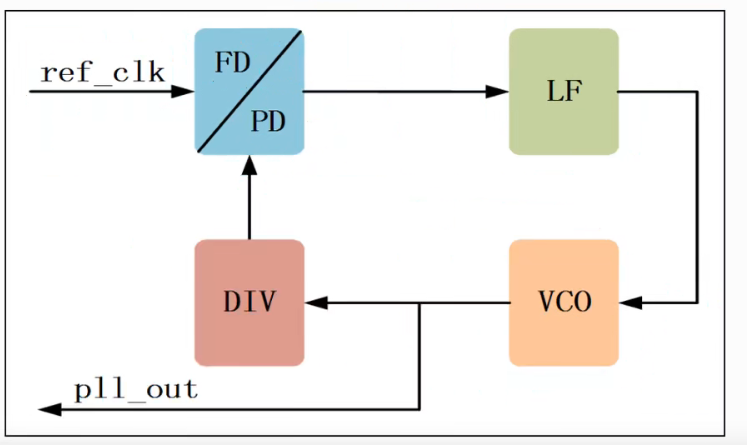

PLL的倍频

DIV 分频器

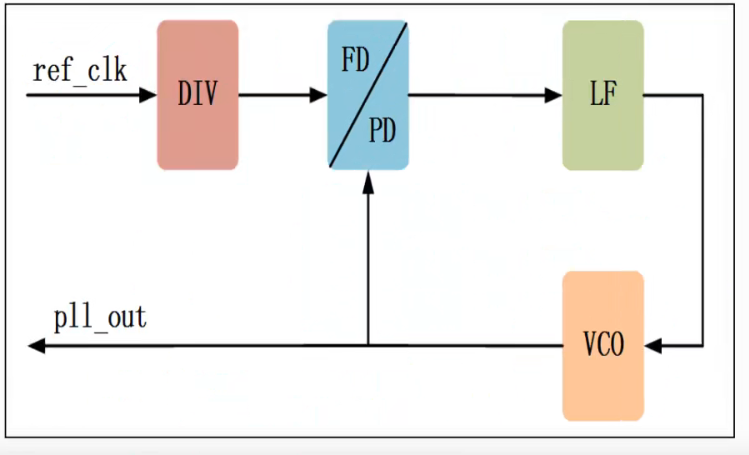

PLL的分频

PLL IP核配置

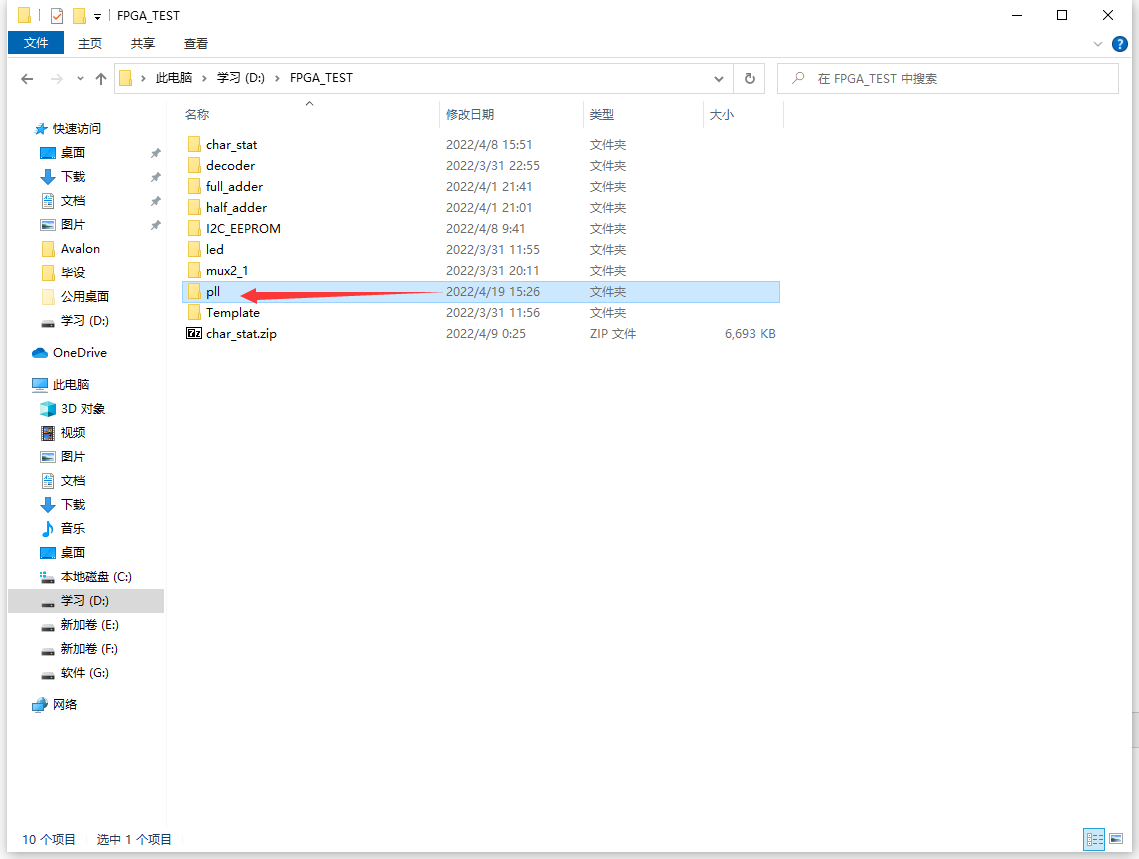

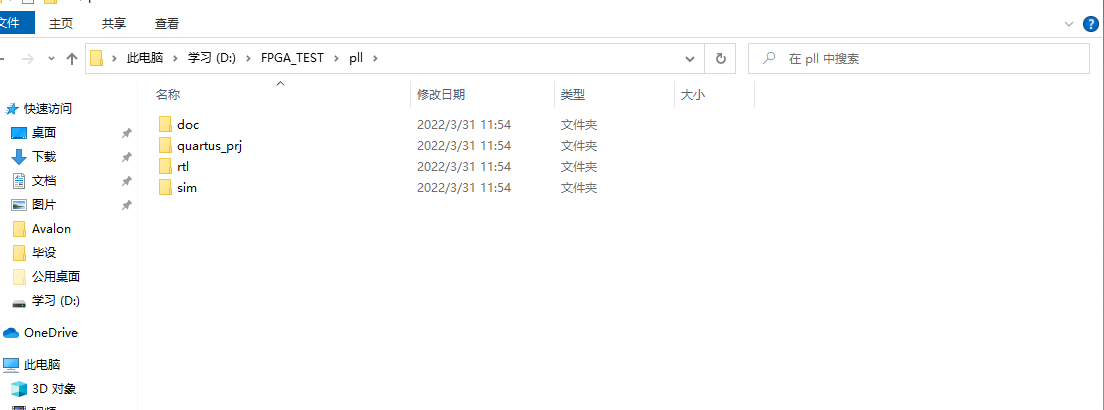

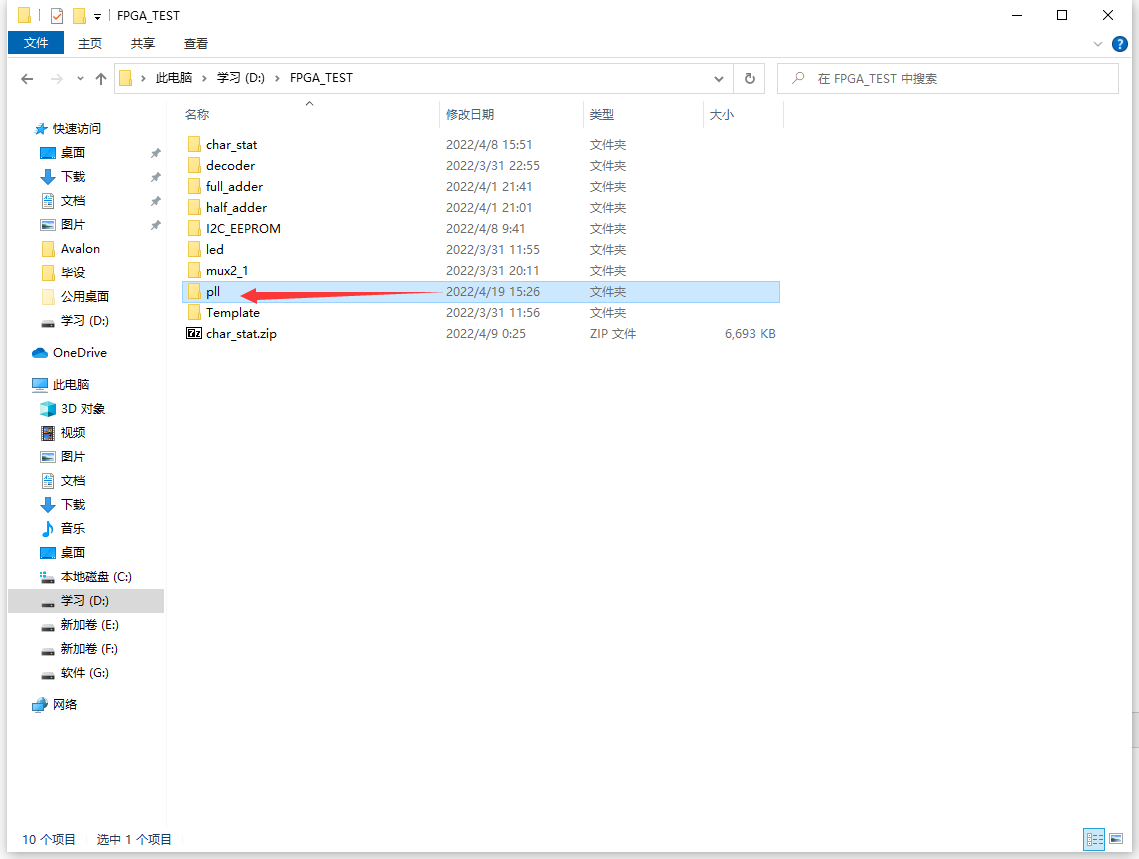

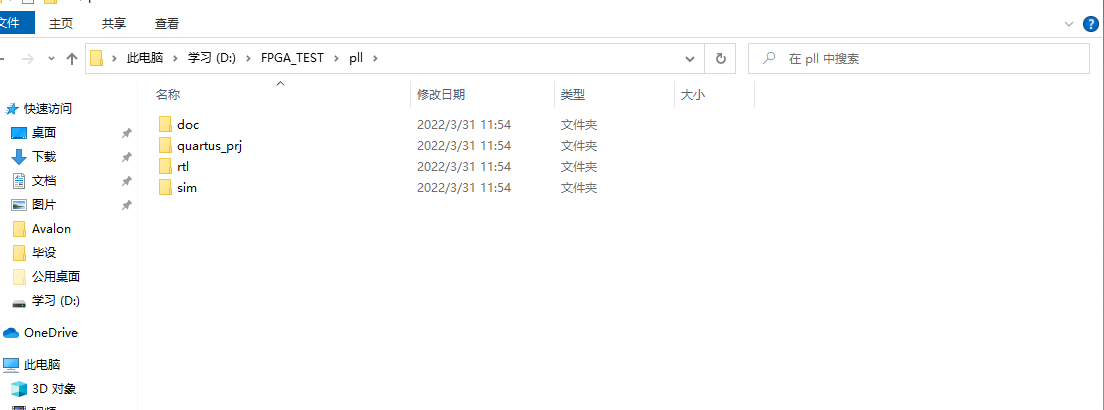

建立文件体系

建立实验工程

使用Quartus Prime Standar Edition 软件

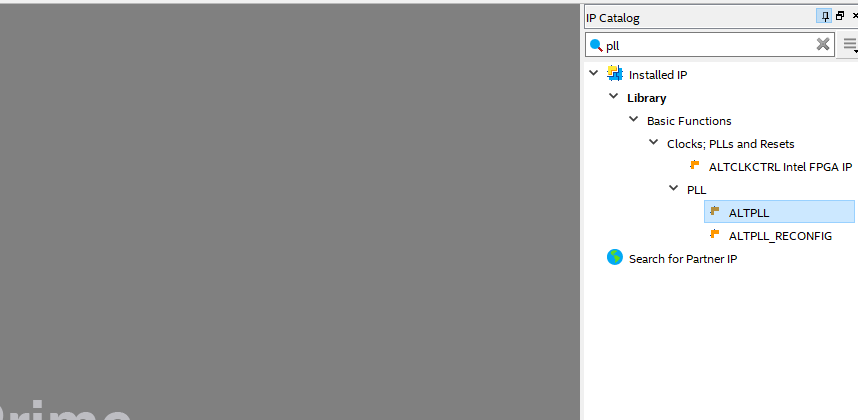

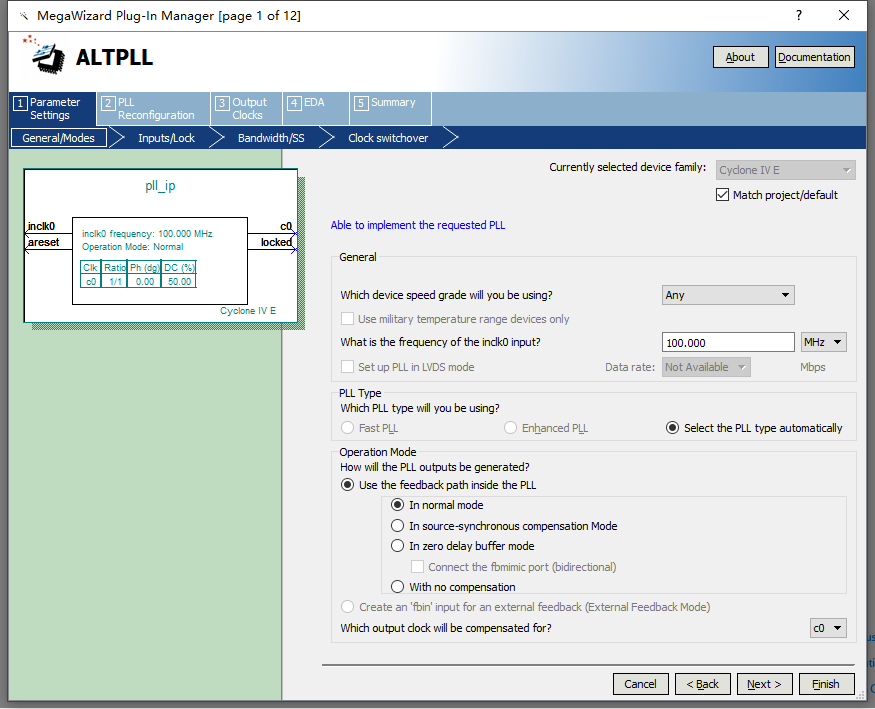

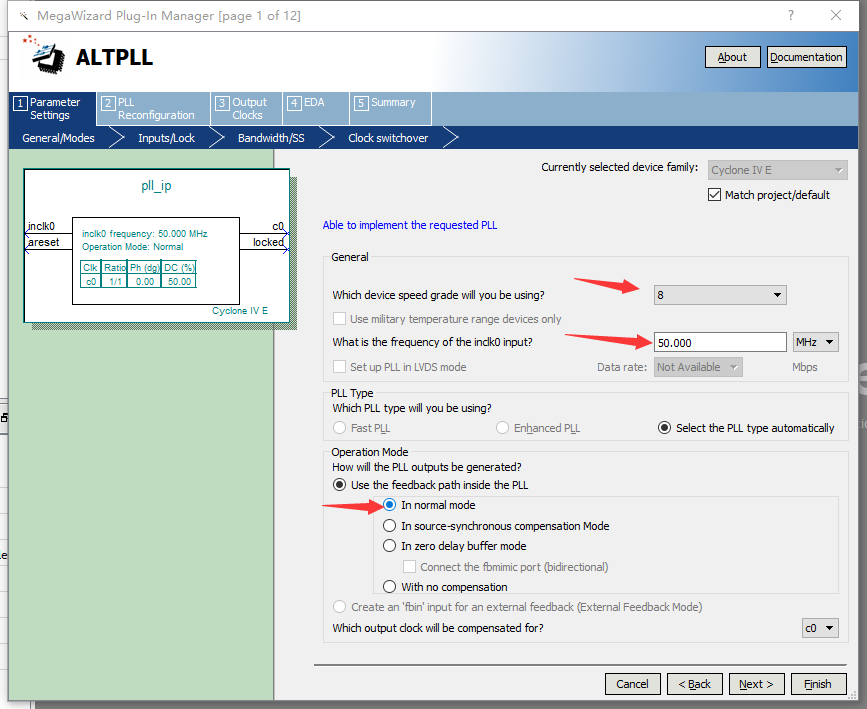

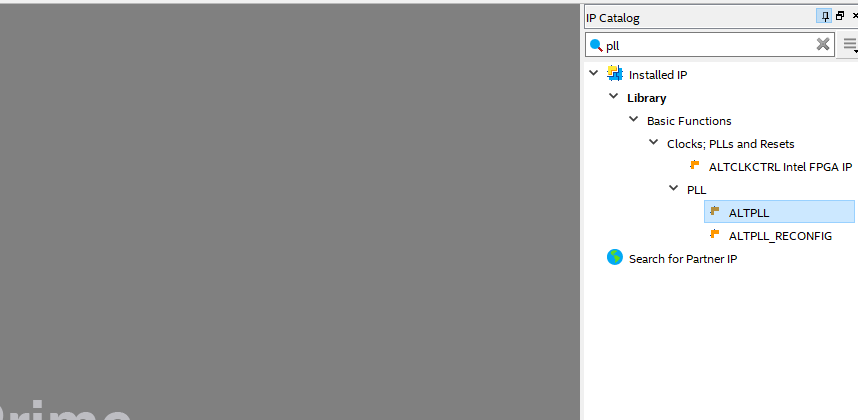

在IP Catalog 搜索框内输入pll,选择ALTPLL

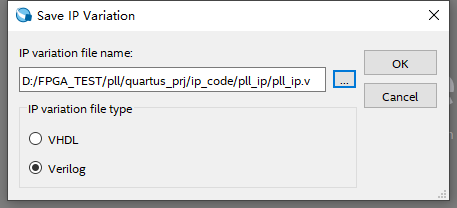

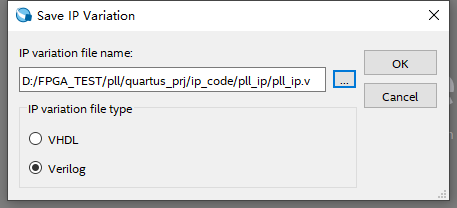

点击.. 在pll工程文件夹内建立pll_ip.v文件,选择OK

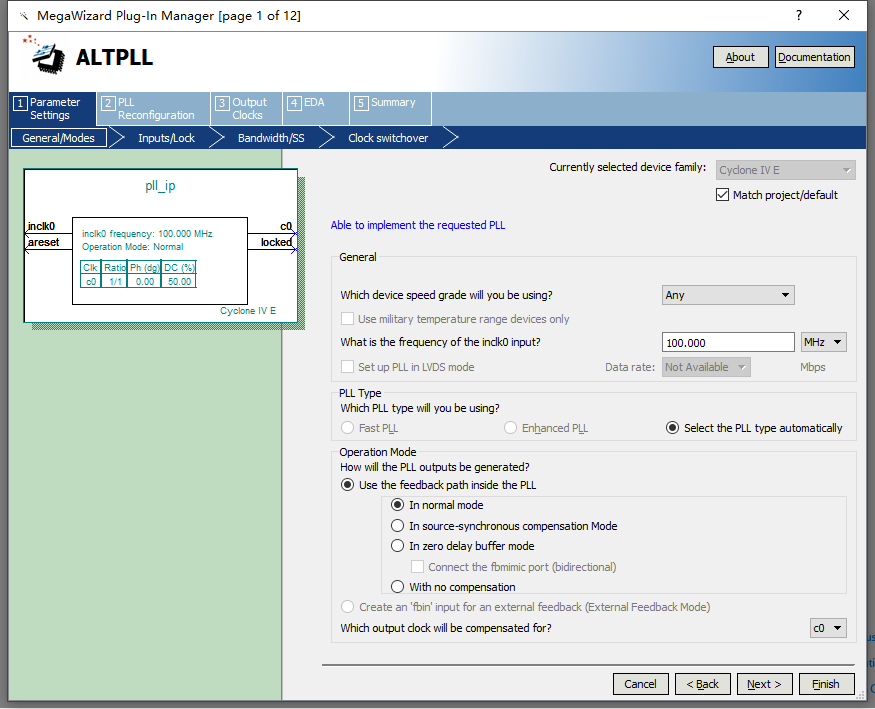

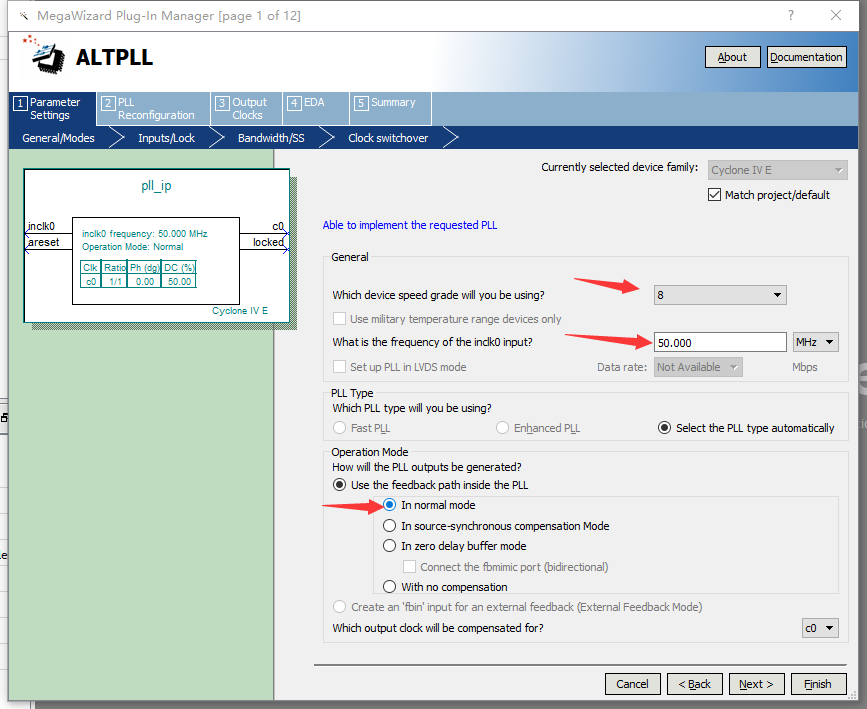

会弹出参数配置界面

参数设置

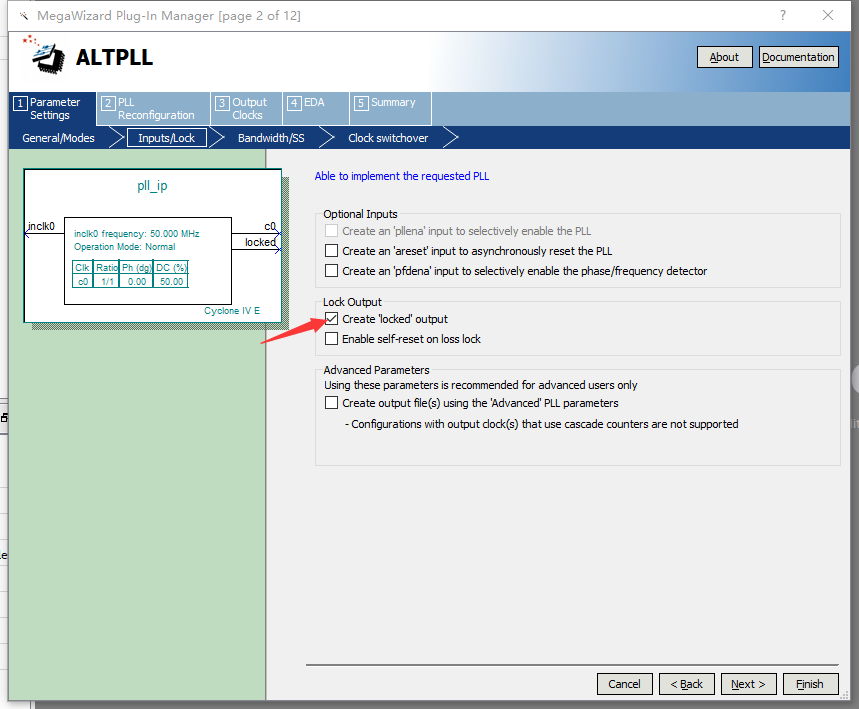

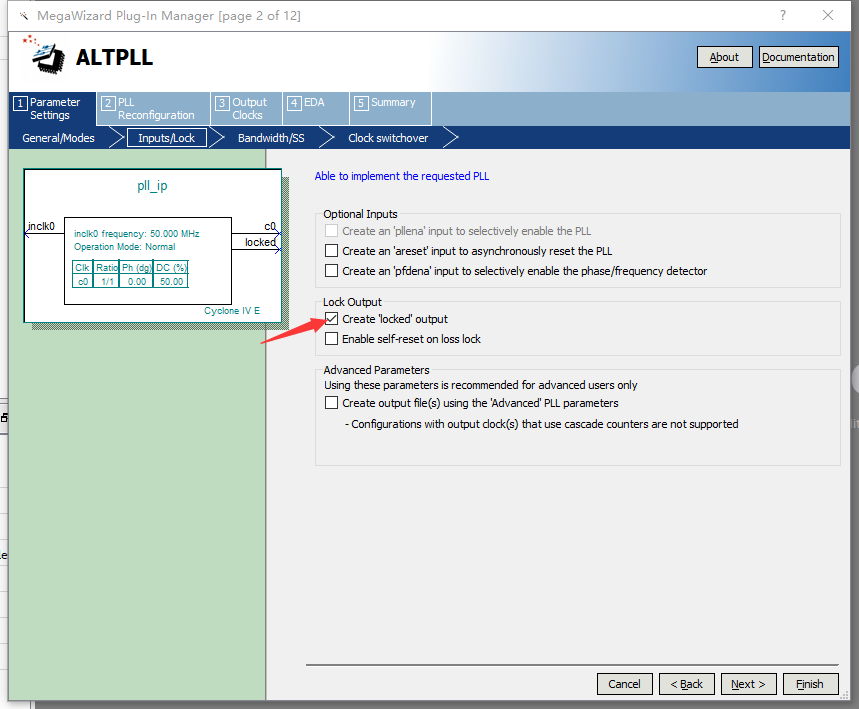

点击next

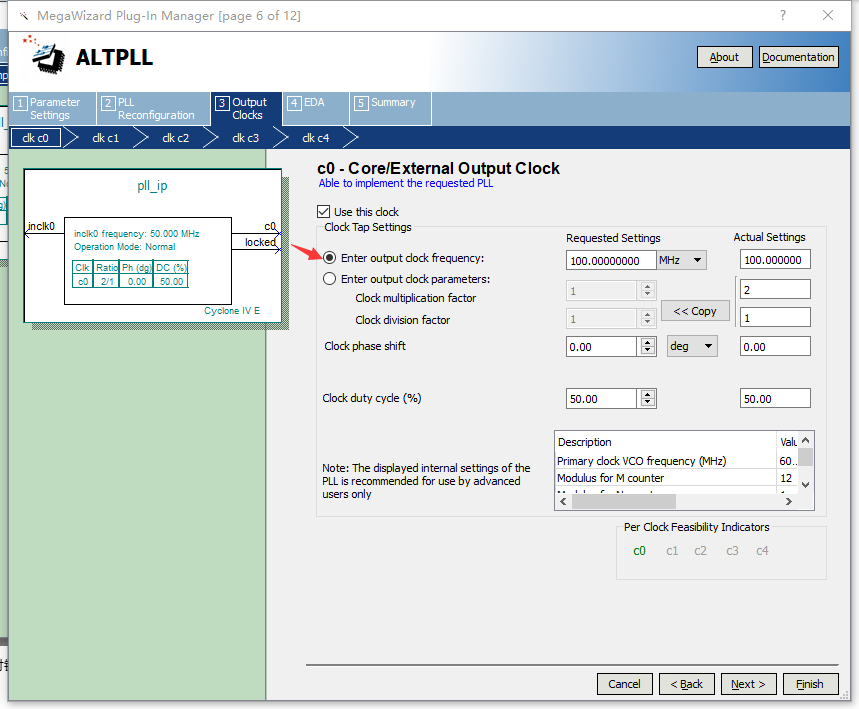

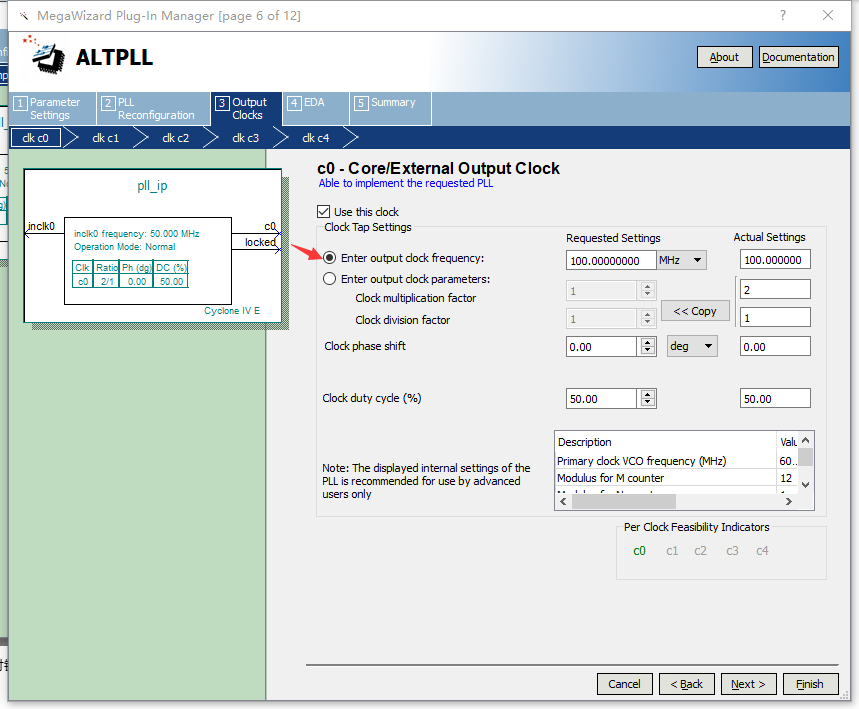

点击next直到PLL输出时钟设置界面,clk0实现2倍频

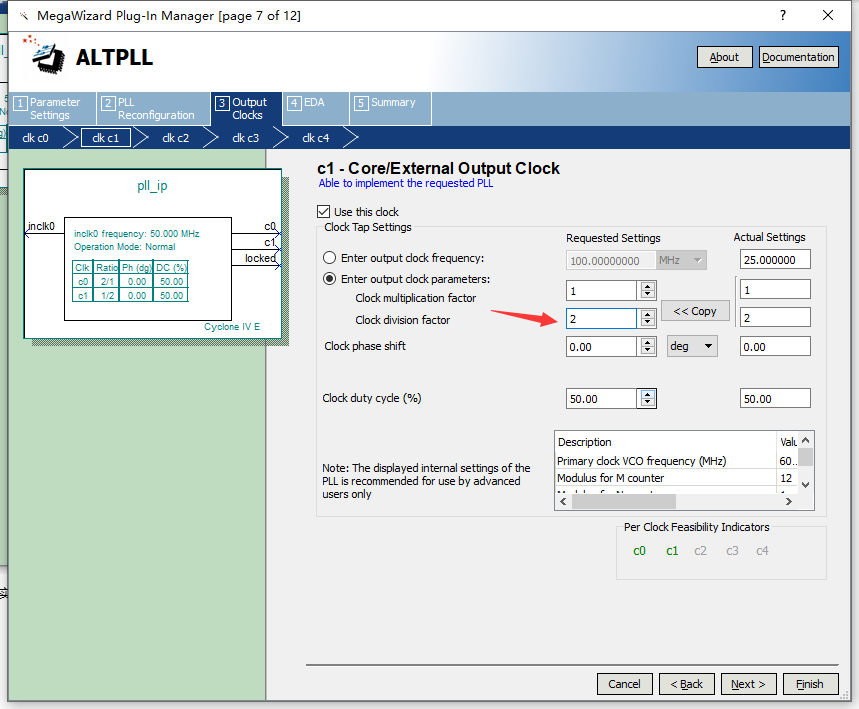

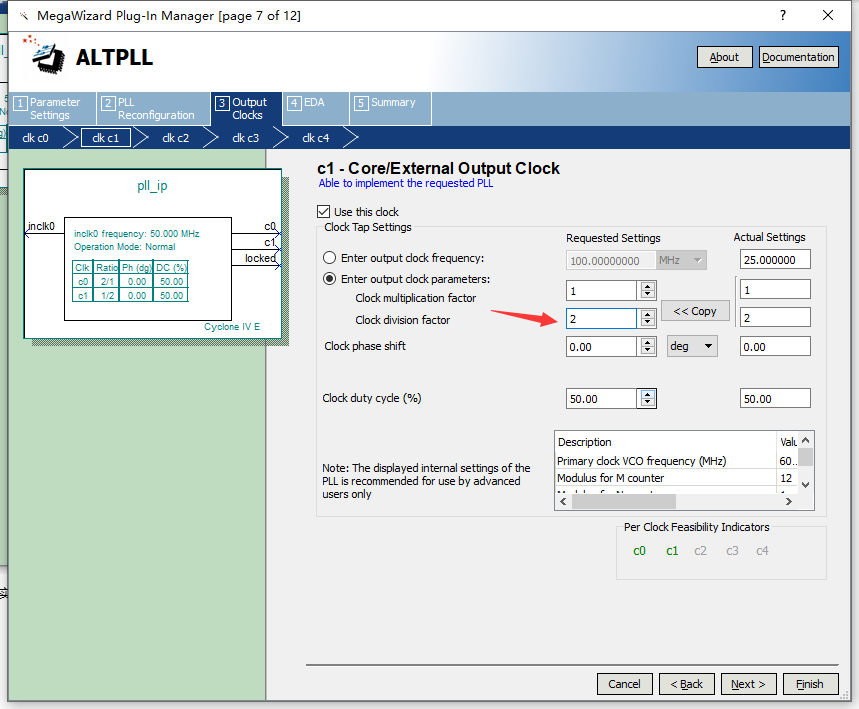

点击next设置clk1,clk实现2分频

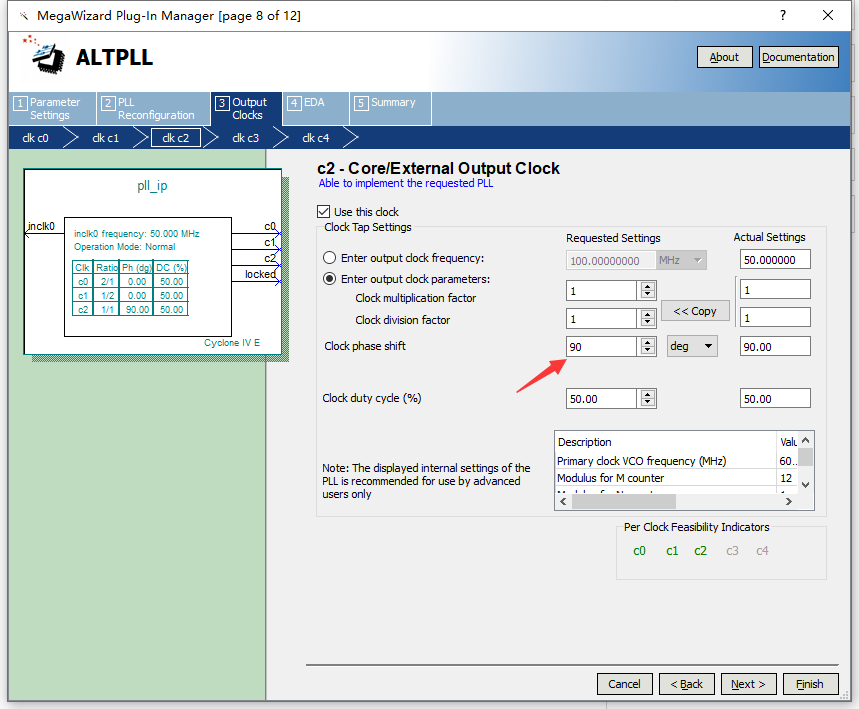

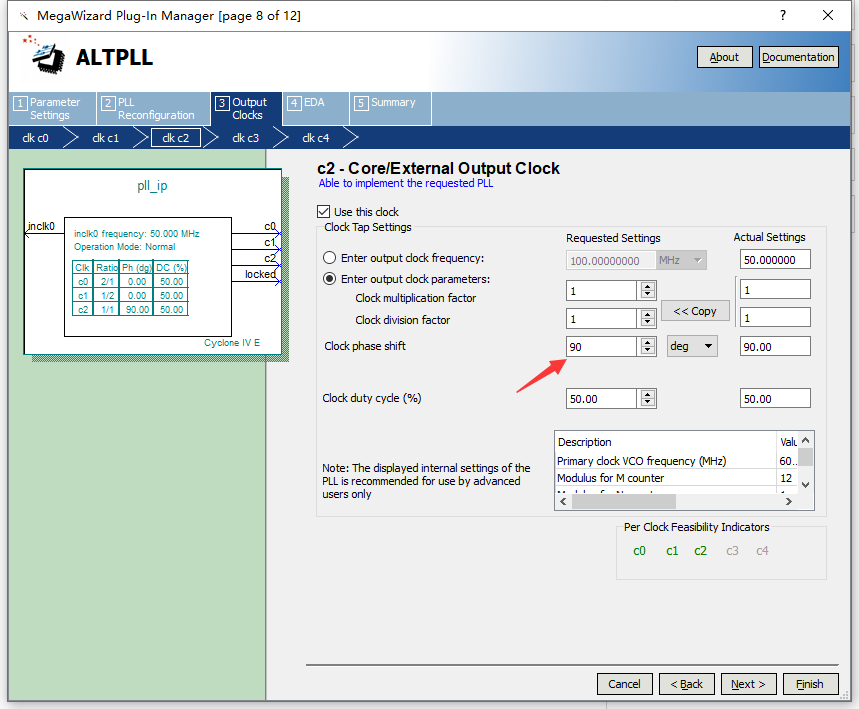

点击next 设置clk2,相移90度

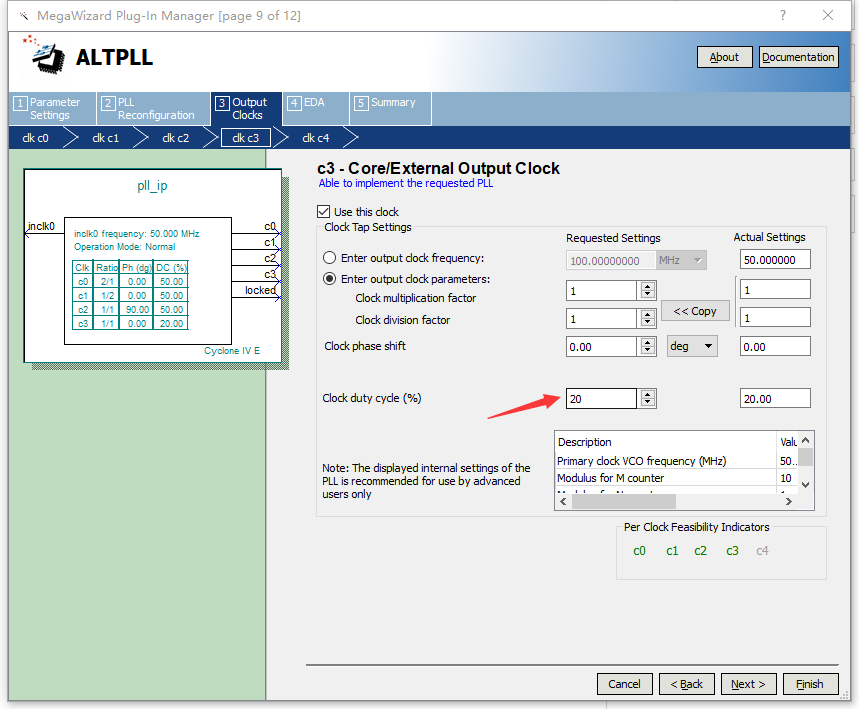

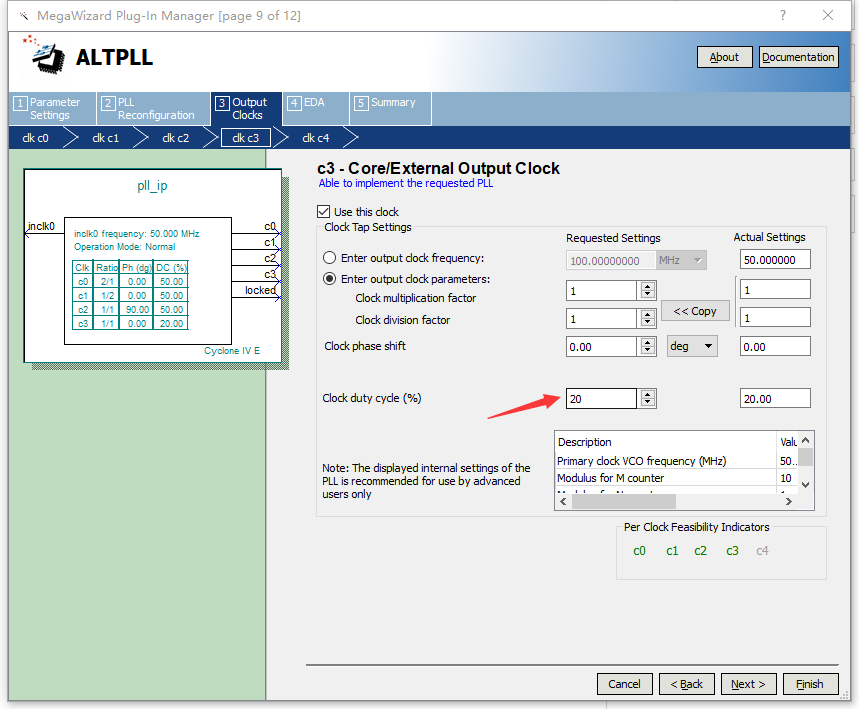

点击next设置clk3,占空比为20%

点击next 到summary界面,输出实例化文件,点击fish。

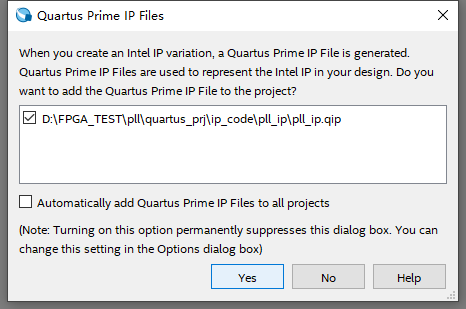

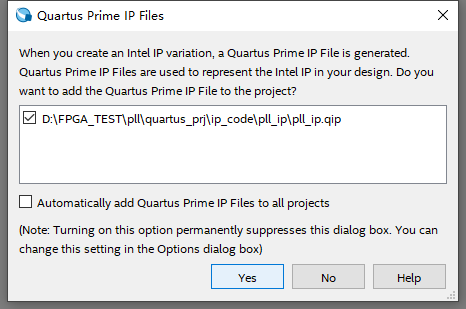

点击yes

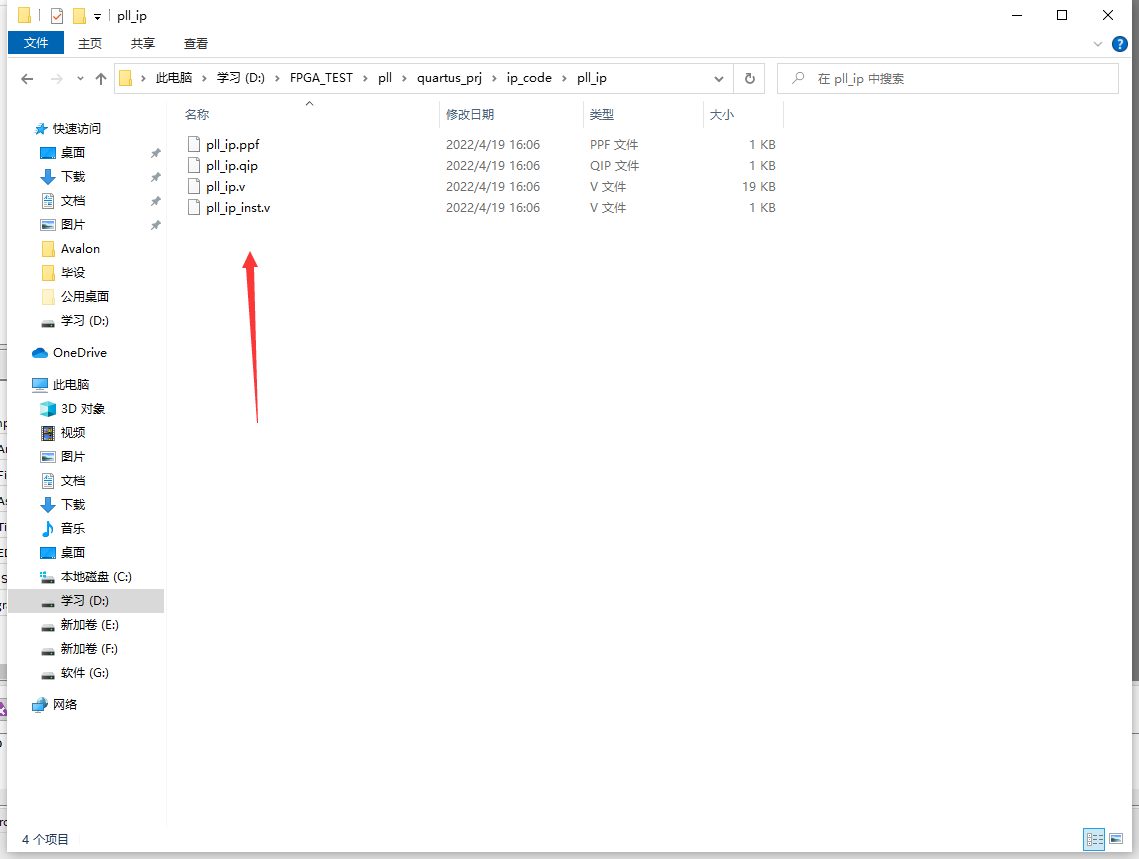

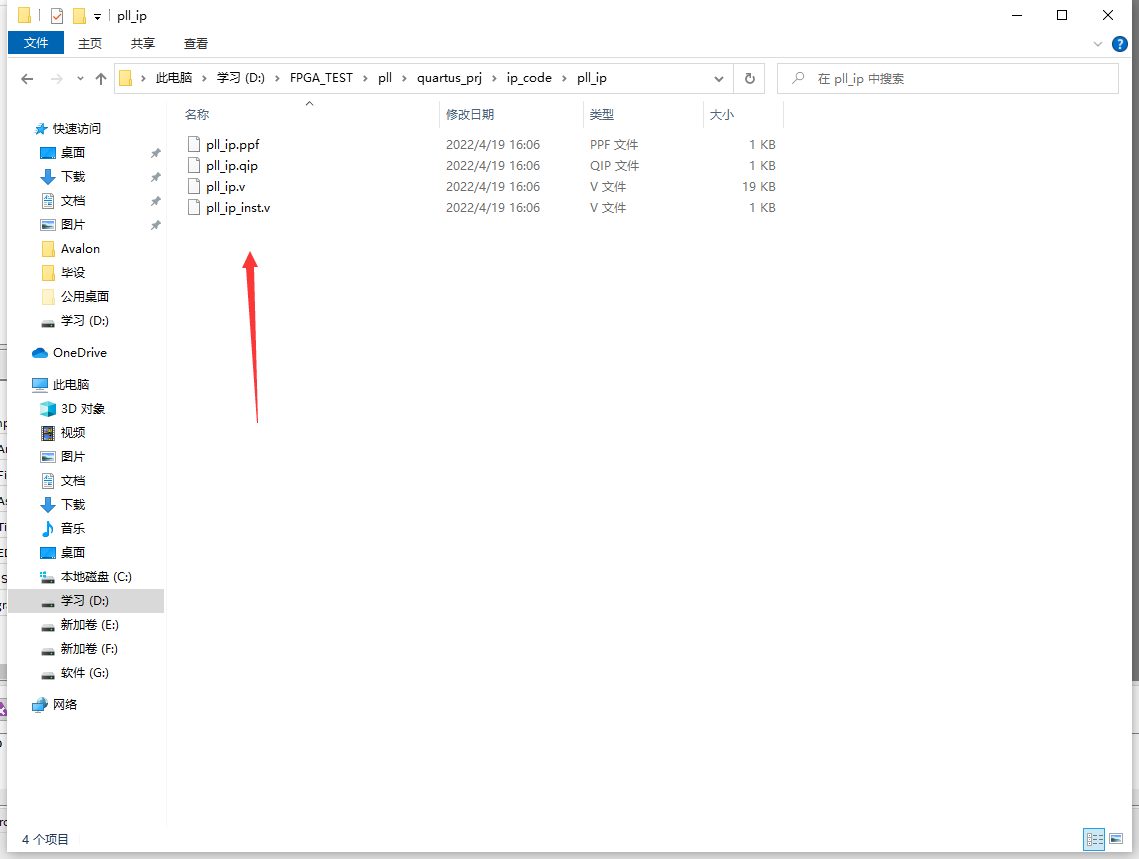

打开文件夹,已经生成了一些文件

回到工程中,编写代码

// Filename﹕ pll.v

// Author﹕YMY

// Description﹕PLL ip核调用

// Calledby﹕/

// RevisionHistory﹕22-04-19

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

module pll(

input wire sys_clk , //系统时钟50MHZ

output wire clk_mul_2 , //2倍频

output wire clk_div_2 , //2分频

output wire clk_pha_90 , //相位偏移90度

output wire clk_duc_20 , //占空比为20%

output wire locked //锁定信号

);

pll_ip pll_ip_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div_2 ),

.c2 ( clk_pha_90 ),

.c3 ( clk_duc_20 ),

.locked ( locked )

);

endmodule

仿真代码

// Filename﹕ tb_pll.v

// Author﹕YMY

// Description﹕PLL ip核调用测试

// Calledby﹕/

// RevisionHistory﹕22-04-19

// Revision1.0

// Email﹕

// Company﹕

// Copyright(c) YMY, All right reserved

`timescale 1ns/1ns

module tb_pll();

reg sys_clk ;

wire clk_mul_2 ;

wire clk_div_2 ;

wire clk_pha_90 ;

wire clk_duc_20 ;

wire locked ;

initial sys_clk = 1'b1 ;

always #10 sys_clk =~sys_clk ;

pll pll_inst

(

. sys_clk (sys_clk ), //系统时钟50MHZ

. clk_mul_2 (clk_mul_2 ), //2倍频

. clk_div_2 (clk_div_2 ), //2分频

. clk_pha_90 (clk_pha_90 ), //相位偏移90度

. clk_duc_20 (clk_duc_20 ), //占空比为20%

. locked (locked ) //锁定信号

);

endmodule

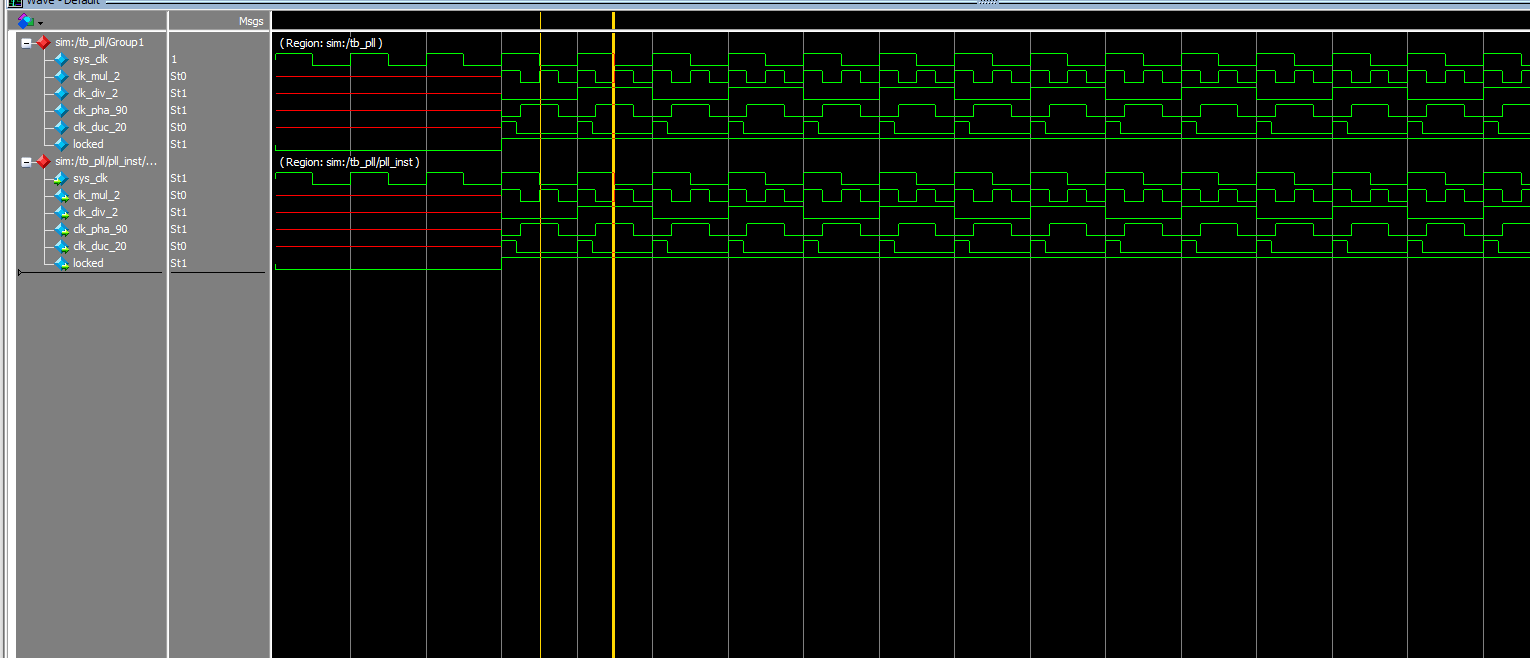

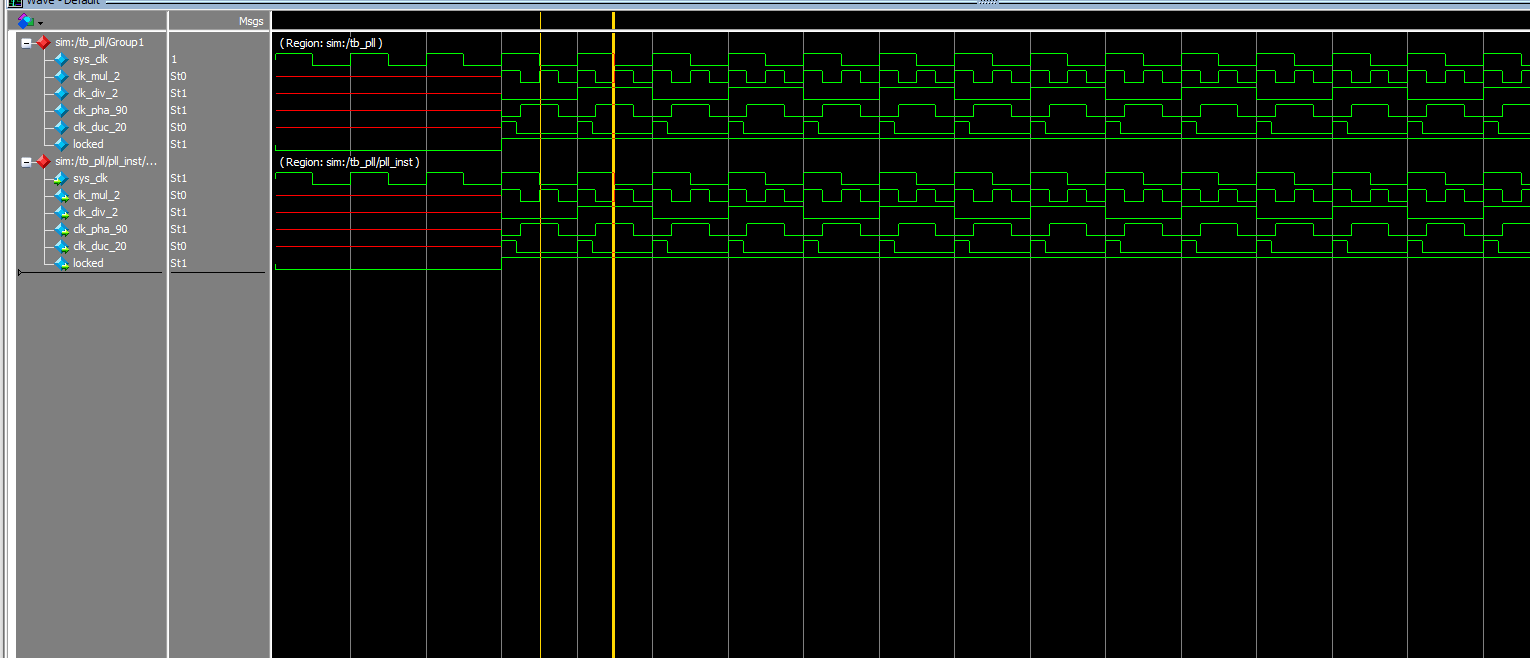

仿真波形