SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。

SDRAM总存储容量 = L-Bank的数量×行数×列数×存储单元的容量,例如该款SDRAM的行地址13bit,列地址9bit,4个bank,16bit数据,所以它的容量 = 4 × 2^13 × 2^9 × 16 = 4 × 4Mb × 16 = 256Mb = 32MB

操作步骤:1.芯片初始化 2.行激活 3.列读写 4.读数据 5.写数据 6.突发长度 7.预充电 8.刷新 9.数据掩码

读操作

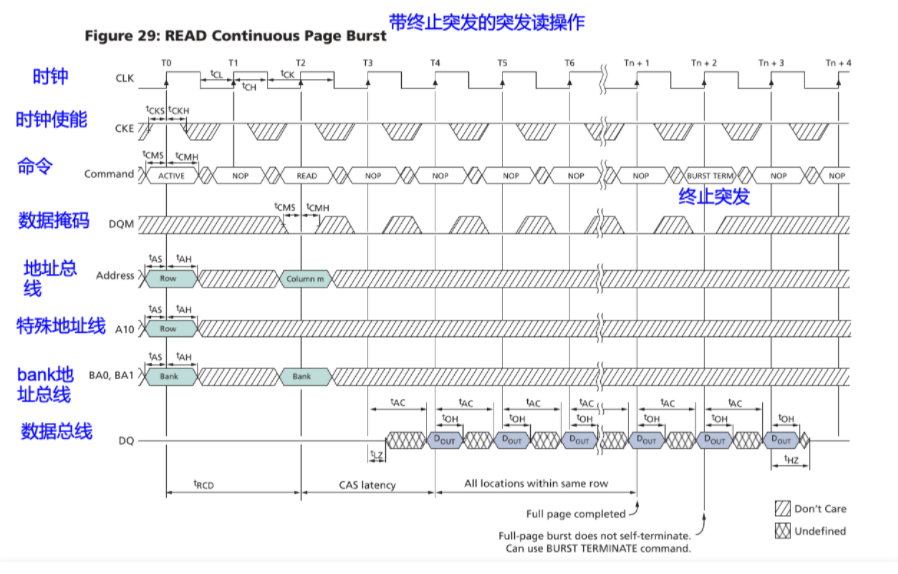

全页突发读操作

时序图

各信号说明如下:

CK:工作时钟,具体时钟频率视不同的芯片而不同

CKE:时钟使能,在整个突发读过程中都需要拉高(实际上除了在休眠模式拉低,其他操作全需要拉高)

COMMAND:SDRAM命令,由4根线拼接而成,分别是CS#(片选信号),RAS#(行选通信号),CAS#(列选通信号),WE#(写使能信号),通过这4根命令线,再结合SDRAM的地址、输入输出数据等,就可以对SDRAM进行各种命令操作

DQM/DQML,DQMU:数据掩码,通过数据掩码可以实现对输入或输出数据的某一位进行“掩埋”,也就是使某一位失效

A[9:0],A[12:11]:数据地址线,同时也可用来设置模式寄存器

A10:数据地址线,同时也可以用来使能一些具体操作,比如控制自动预充电使能、使能预充电bank数量

BA[1:0]:bank地址

DQ数据:数据总线,突发读过程中需要根据时序获取数据总线上SDRAM输出的数据

通过对时序图的分析可以总结出初始化过程如下:

1.发送激活指令,同时在bank总线输出想要写入数据的bank地址,在地址总线输出写入数据的行地址,所以该操作也称之为 “ 行激活 ”

2.发送激活指令后需要等待一定的时间,即tRCD,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

3.等待结束后发送读指令,在地址总线输出要读取数据的列首地址,然后等待潜伏期(CL,CAS latency)个时钟周期

4.潜伏期结束后,数据总线开始输出数据,此后每个周期均有数据输出,直到向SDRAM发送突发终止指令,结束这次突发读取,由此可实现突发长度的控制(不能超过一行数据的最大数,即2*9=512个数据)

5.发送预充电指令对所有BANK进行预充电操作,A10拉高即是选中所有BANK

6.进行预充电操作后需要等待一定的时间,即tRP,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

7.tRP时间结束后,一次突发读操作完成

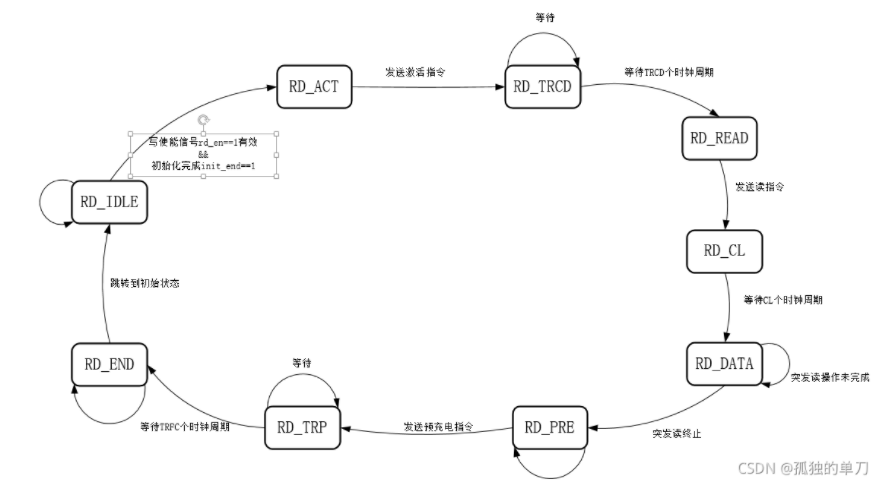

状态机

RD_IDLE: 初始状态,当初始化完成信号拉高(初始化完成)且仲裁模块发送突发读使能信号后,跳转至下一状态RD_ACT,在此状态发送NOP指令

RD_ACT: 行激活状态,只维持一个时钟周期然后跳转到下一状态RD_TRCD,发送行激活指令(ACTIVE)+bank地址+行地址

RD_TRCD:行激活等待状态在此状态等待时间满足TRCD后就跳转到下一个状态RD_WR,在此状态发送NOP指令

RD_WR: 列读写状态,只维持一个时钟周期然后跳转到下一状态RD_CL,发送读指令(READ)+bank地址+列首地址

RD_CL: 潜伏期等待状态在此状态等待时间满足CL后就跳转到下一个状态RD_DATA,在此状态发送NOP指令

RD_DATA: 数据读取状态,在此状态先发送NOP指令 ,同时将数据总线上的数据寄存;当所有要读取的数据都输出后(提前CL个时钟周期,因为数据的读取会滞后CL个时钟周期),发送突发终止指令(BURST TERM),终结读操作,跳转到RD_PRE状态

RD_PRE: 发送预充电指令状态,只维持一个时钟周期然后跳转到下一状态RD_TRP,发送行预充电指令(PRECHARGE)+A10拉高

RD_TRP: 预充电指令等待状态、在此状态等待时间满足TRP后就跳转到下一个状态RD_END,在此状态发送NOP指令

RD_END: 该状态拉高突发写标志完成信号wr_end一个周期,告诉仲裁模块写操作完成,以便仲裁模块对刷新、写、读等请求进行仲裁(防止时序冲突)

写操作

全页突发写操作

1.发送激活指令,同时在bank总线输出想要写入数据的bank地址,在地址总线输出写入数据的行地址,所以该操作也称之为 “ 行激活 ”

2.发送激活指令后需要等待一定的时间,即tRCD,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

3.等待结束后发送写指令,同时在在bank总线输出想要写入数据的bank地址,在地址总线输出写入数据的列首地址,并且在数据总线输出要写入SDRAM的第一个数据,所以该操作也称之为 “ 列读写 ”

4.每个周期多输出空指令,但数据总线一直输出想要输出的数据

5.在所有数据输出完成后的下一个周期输出 “ 突发终止 ”指令,结束这次突发写入,由此可实现突发长度的控制(不能超过一行数据的最大数,即2*9=512个数据)

6.发送预充电指令对所有BANK进行预充电操作,A10拉高即是选中所有BANK

7.进行预充电操作后需要等待一定的时间,即tRP,在此期间同样需要发送NOP空指令(发送空指令是为了防止对SDRAM进行误操作)

8.tRP时间结束后,一次突发写操作完成

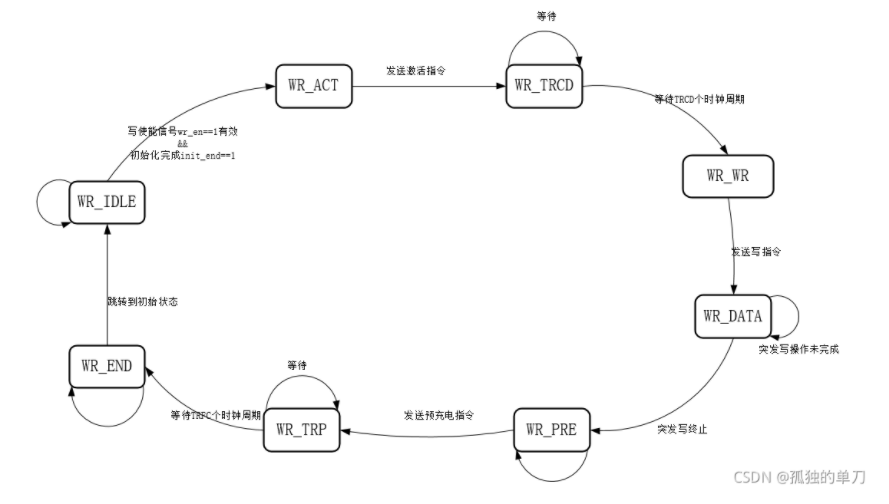

状态机

WR_IDLE: 初始状态,当初始化完成信号拉高(初始化完成)且仲裁模块发送突发写使能信号后,跳转至下一状态WR_ACT,在此状态发送NOP指令

WR_ACT: 行激活状态,只维持一个时钟周期然后跳转到下一状态WR_TRCD,发送行激活指令(ACTIVE)+bank地址+行地址

WR_TRCD:行激活等待状态在此状态等待时间满足TRCD后就跳转到下一个状态WR_WR,在此状态发送NOP指令

WR_WR: 列读写状态,只维持一个时钟周期然后跳转到下一状态WR_DATA,发送列读写指令(WRITE)+bank地址+列首地址

WR_DATA: 数据写入状态,在此状态先发送NOP指令 ,同时在数据总线上输出数据;当所有要写入的数据都输出后,发送突发终止指令(BURST TERM),终结写操作,跳转到WR_PRE状态

WR_PRE: 发送预充电指令状态,只维持一个时钟周期然后跳转到下一状态WR_TRP,发送行预充电指令(PRECHARGE)+A10拉高

WR_TRP: 预充电指令等待状态、在此状态等待时间满足TRP后就跳转到下一个状态WR_END,在此状态发送NOP指令

WR_END: 该状态拉高突发写标志完成信号wr_end一个周期,告诉仲裁模块写操作完成,以便仲裁模块对刷新、写、读等请求进行仲裁(防止时序冲突)

————————————————

原文链接:https://blog.csdn.net/wuzhikaidetb/article/details/120397345

原文链接:https://blog.csdn.net/wuzhikaidetb/article/details/120399012