一、实验目的:VIVADO建立一个FPGA开发工程,然后采用时序和计数实现LED的流水灯显示。

二、ZYNQ工程建立

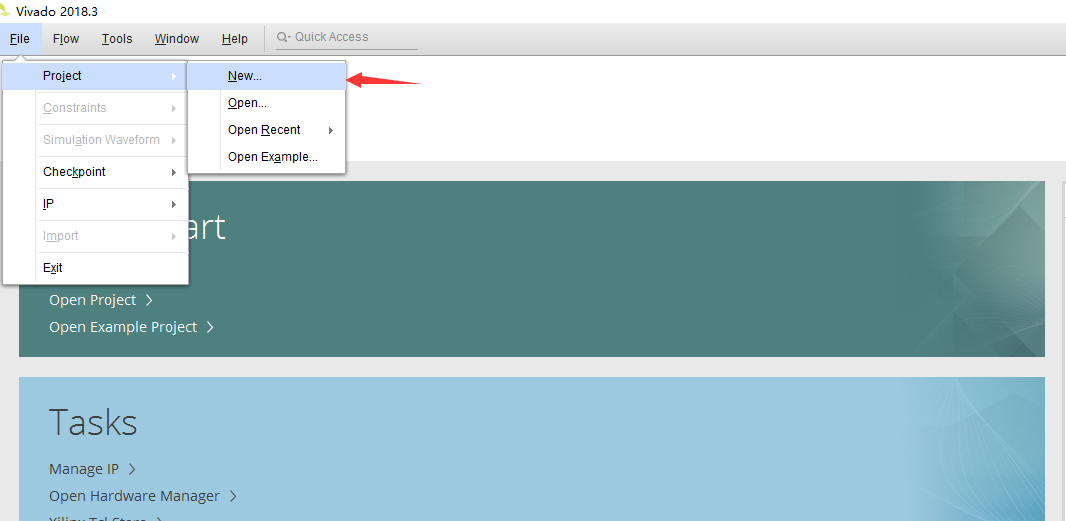

打开Vivado软件,创建新工程

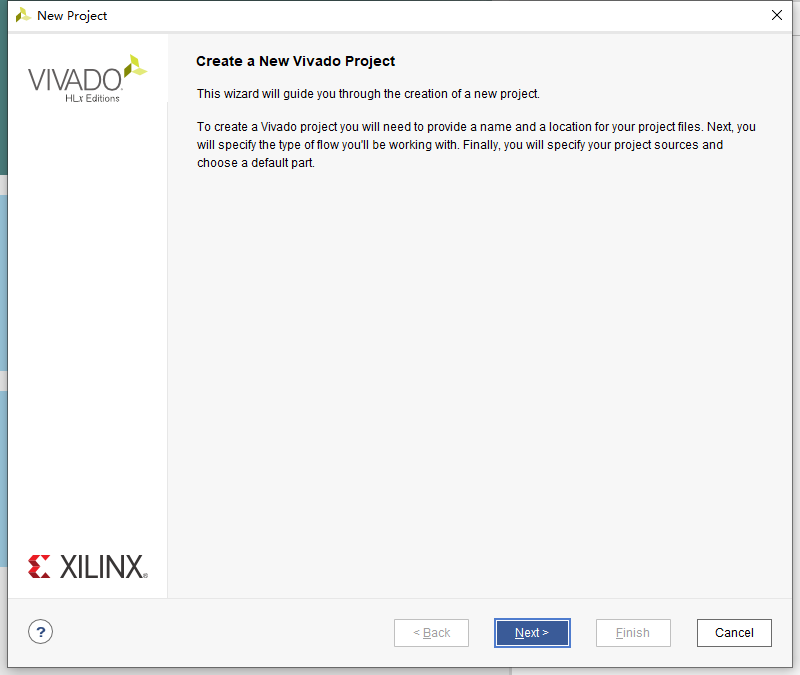

点击next

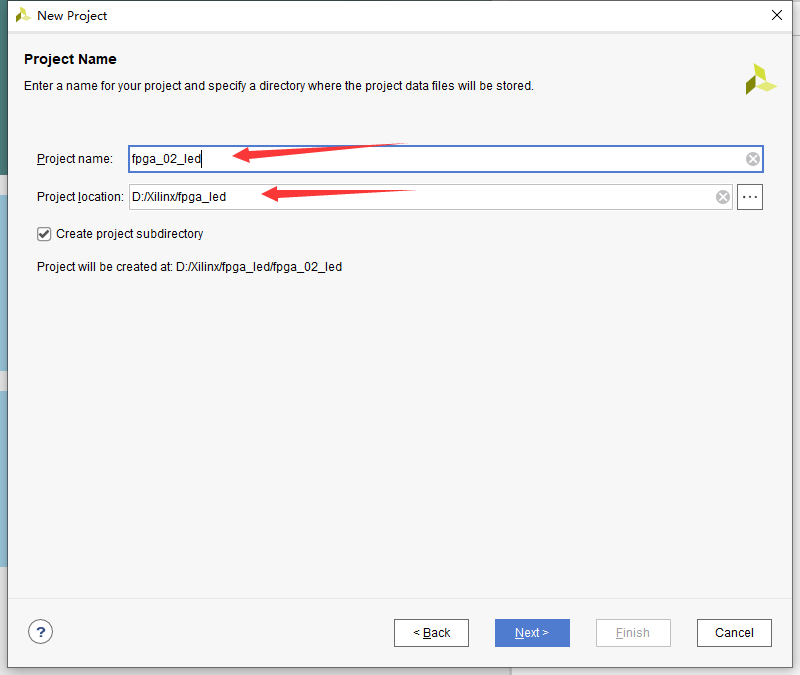

命名工程名,选择工程路径,点击next

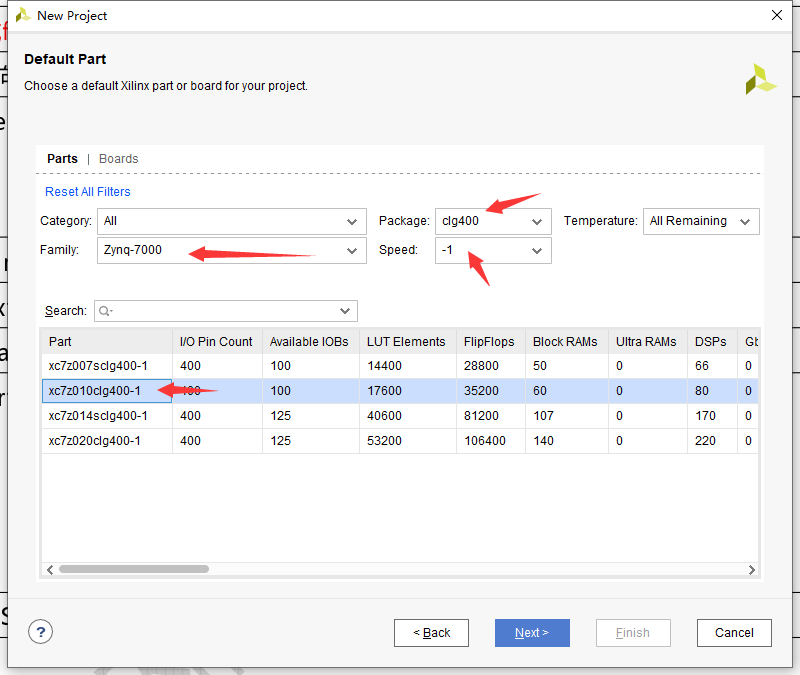

Project Type --next,Add Sources--next,Add Constraints--next,Default Part 界面进行如下配置,使用版本为7010。

点击next,点击finish

三、具体实现步骤

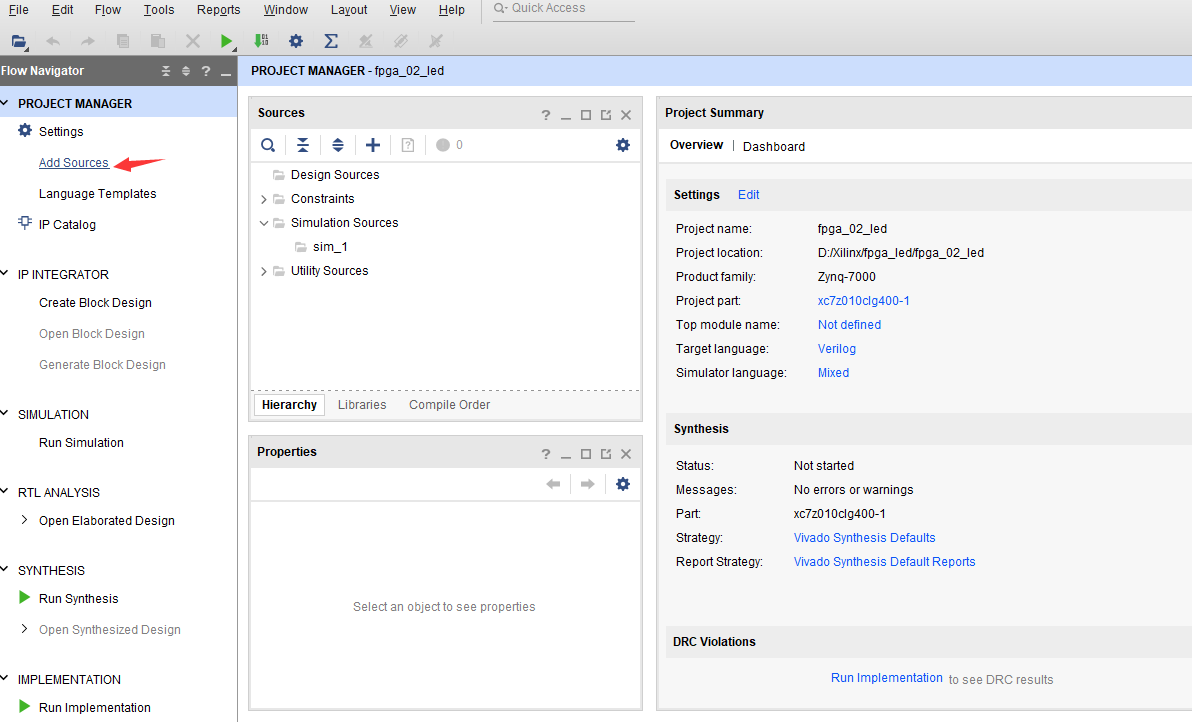

点击Add Sources 添加流水灯代码

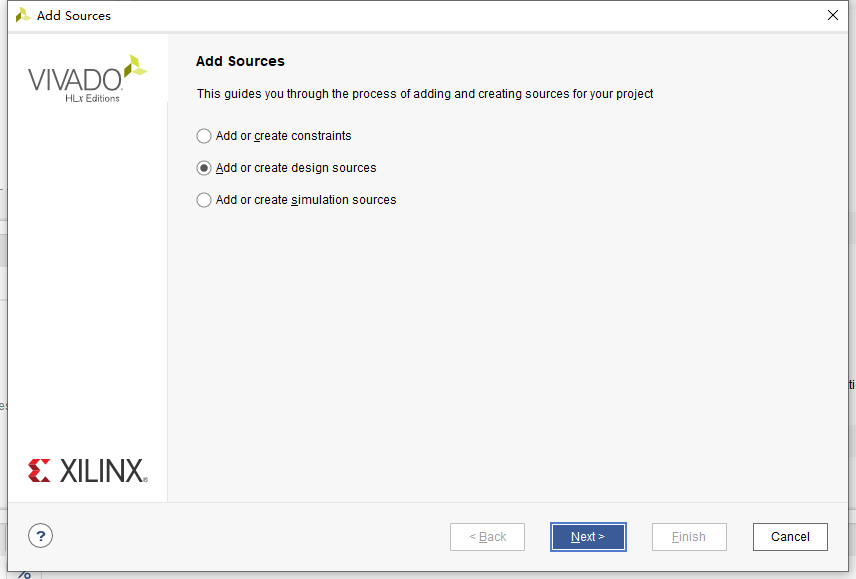

3.选择Add or create designsources,点击next

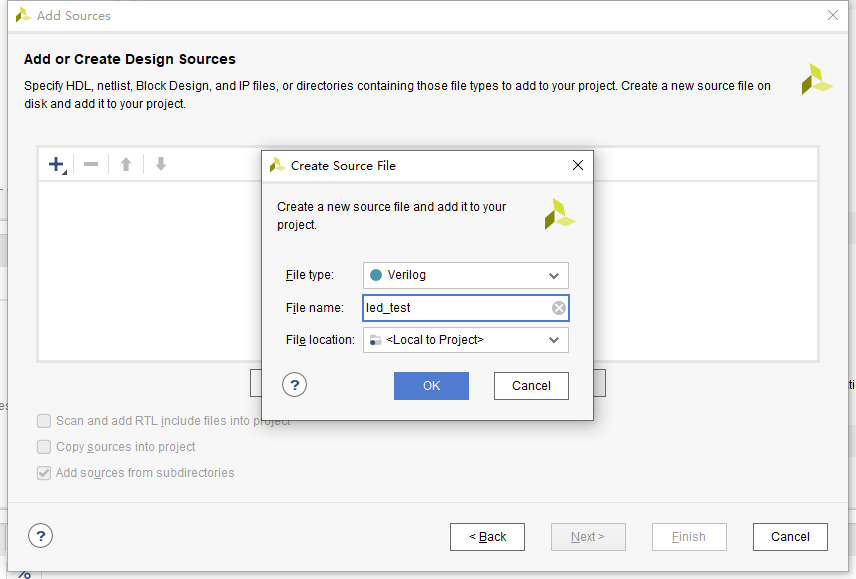

4.选择Create Files,选择Verilog语言,填入文件名,点击ok

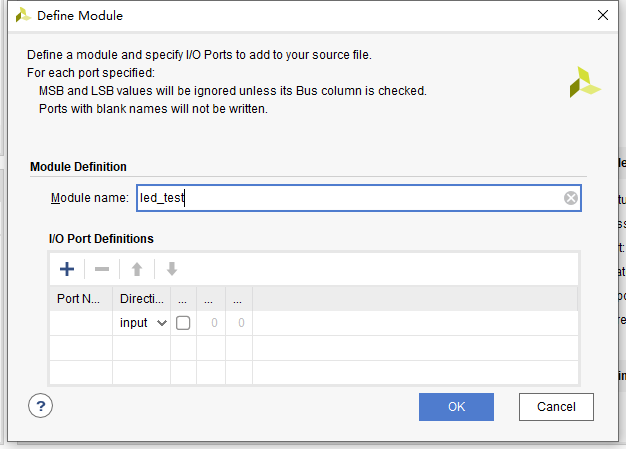

5.点击Finish,点击ok

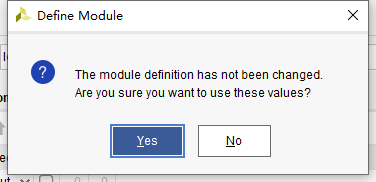

6.点击YES

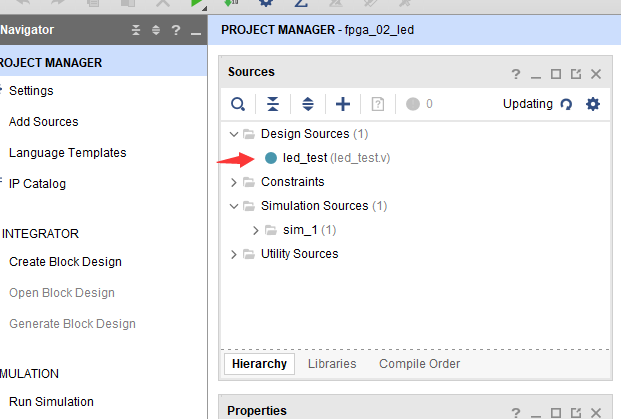

7.可以看见led_test模块已经出现在设计文档中,双击打开编辑代码

8.代码如下

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: yu meng ya

//

// Create Date: 2022/04/29 20:00:42

// Design Name: 流水灯

// Module Name: led_test

// Project Name: fpga_02_led

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module led_stream(

output reg [3:0] led, // LED4 to LED1, 1 on, 0 off

input clk, // FPGA PL clock, 50 MHz

input rst_n // FPGA reset pin

);

reg [31:0] cnt;

reg [1:0] led_on_number;

//clock input 50000000

parameter CLOCK_FREQ =50000000;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1;//change time 0.5s

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

cnt <= 31'd0;

led_on_number <= 2'd0;

end

else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin//计数0.5s

cnt <= 31'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end

always @(led_on_number) begin

case(led_on_number)

0: led <= 4'b0001;

1: led <= 4'b0010;

2: led <= 4'b0100;

3: led <= 4'b1000;

endcase

end

endmodule

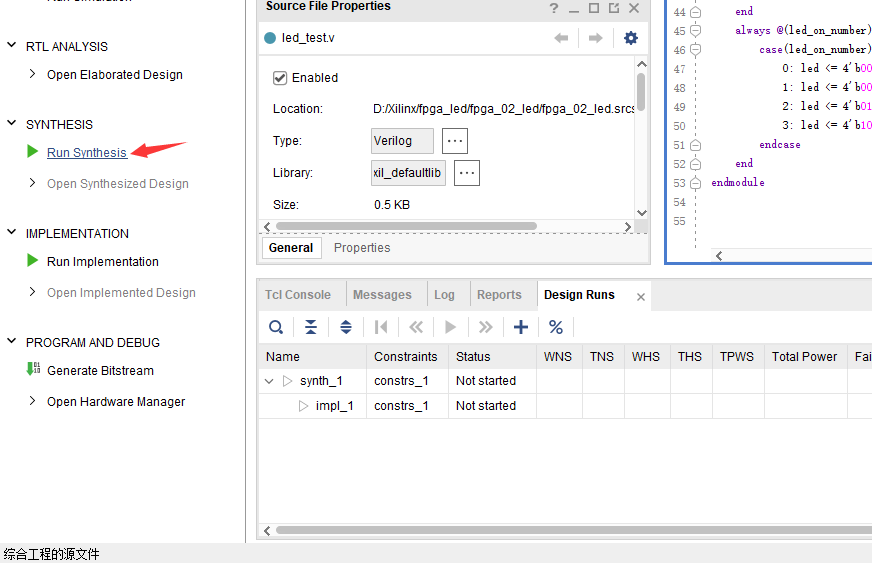

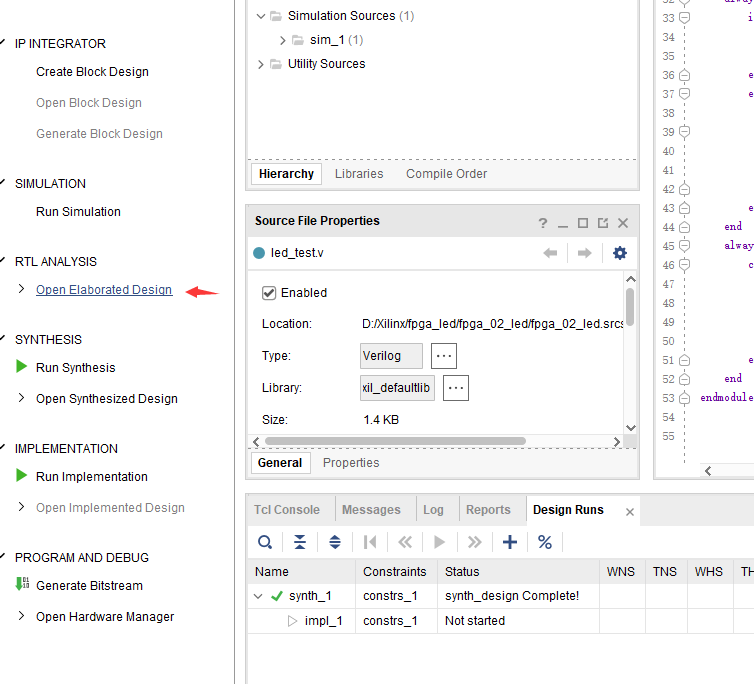

9.开始综合,点击Run Synthesis

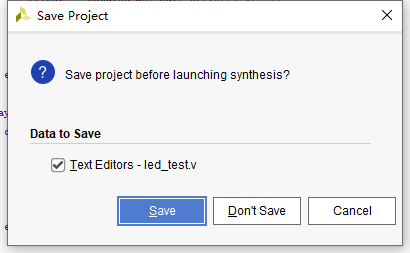

10.选择save

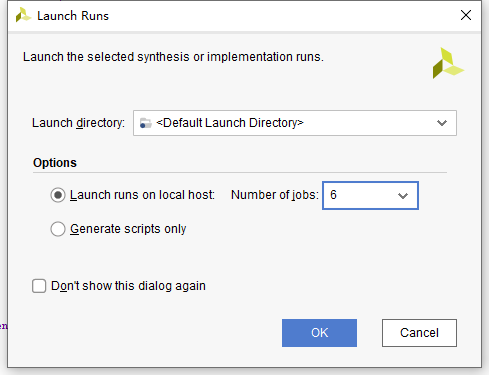

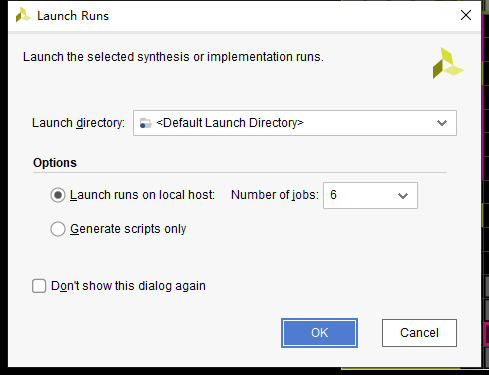

11.由于这里电脑配置是 I7-7700K,四核八线程,所以最多可以选择 8 个。综合过程很耗 CPU 性能,所以如果想要综合过程中流畅使用电脑,可以少选两个线程。选完线程数量,点击 ok。

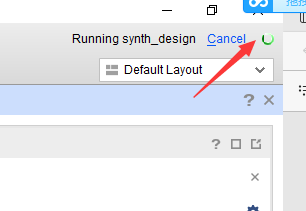

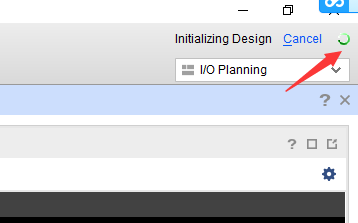

可以看见已经在运行了

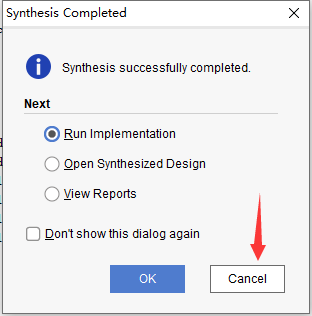

12.选择Cancel

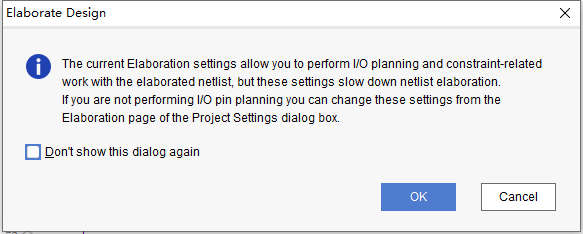

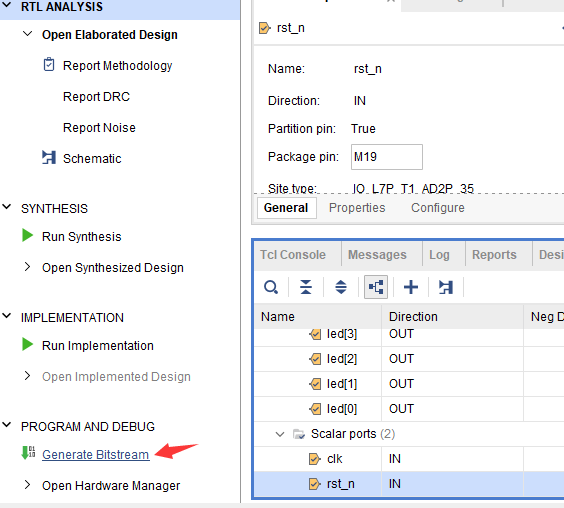

13.引脚绑定,点击open Elaborated Design

14.选择ok

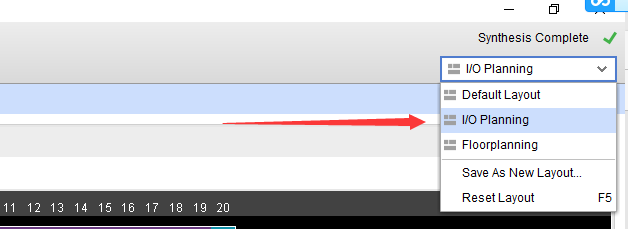

15.选择择 I/O Planning

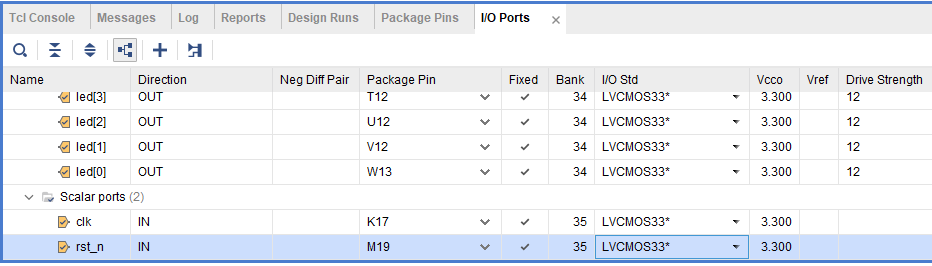

16.引脚绑定,电平标准选择(LVCMOS33)

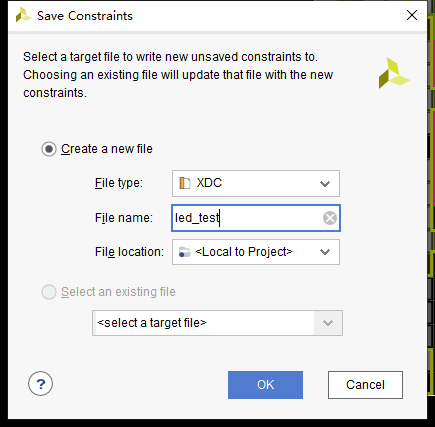

17.Ctrl+s,保持,填写文件名,点击ok

18.PROGRAM AND DEBUG 下面的 Generate Bitestream 生成 BIT 文件。

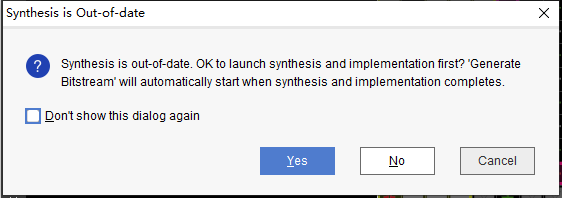

19.点击yes

20.点击ok

21.等待软件运行这些操作结束

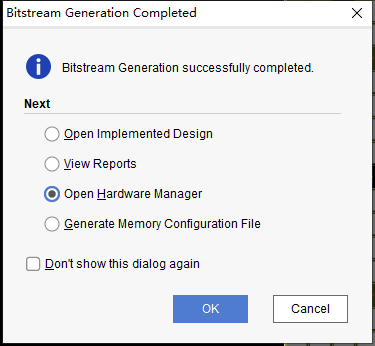

22.点击 Open Hardware Mnager ,点击ok

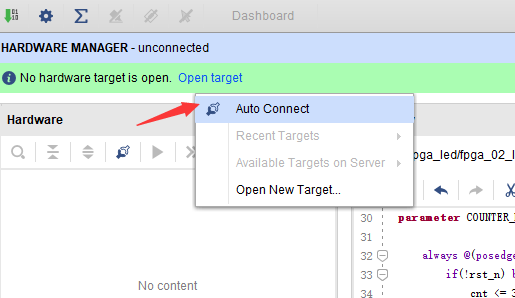

23.弹出的硬件管理界面,这个时候可以插上我们的ZYNQ MINI开发板的下载器USB接口,然后点击 Open target,选择Auto Connect

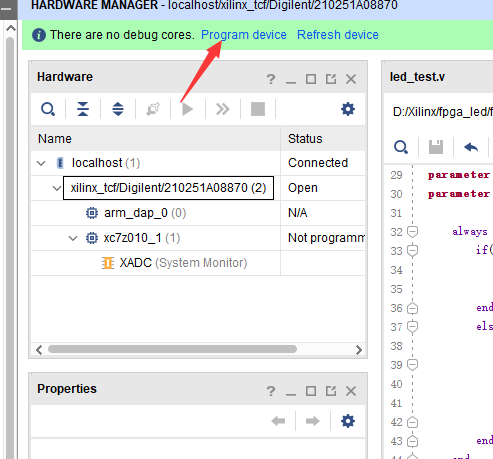

24.可以看到 Hardware 窗口出现了两个设备,一个是 arm 的 dap,一个是 xc7z010 芯片。上方我们点击 Program Device 进行烧写配置

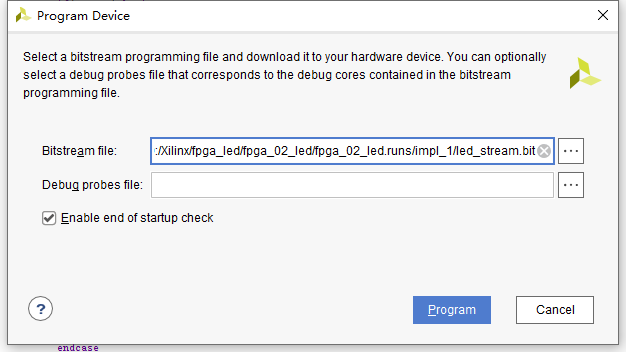

25.保持默认,点击program

26.烧写完成。我们可以看到四个 led 0.5 秒周期流动亮起。