一、实验目的

调用锁相环ip通过输入的50M时钟产生100M甚至更高的时钟源。在学会在Vivado下调用IP核。

实现效果:锁相环时钟输出,最后驱动水流灯模块。

二、ZYNQ工程的建立

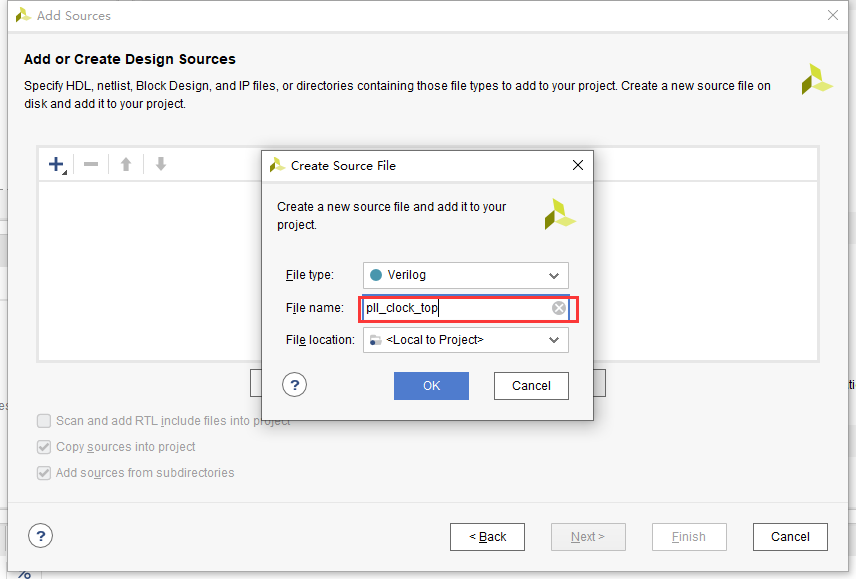

1. 击 Add Sources 添加新建文件:pll_clock_top.v。

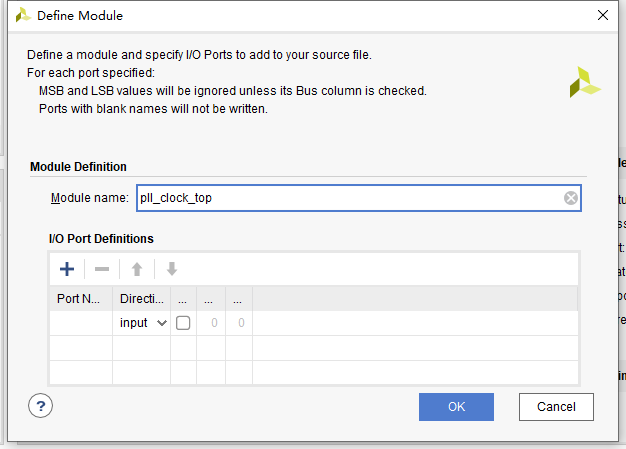

2.模块名pll_clock_top

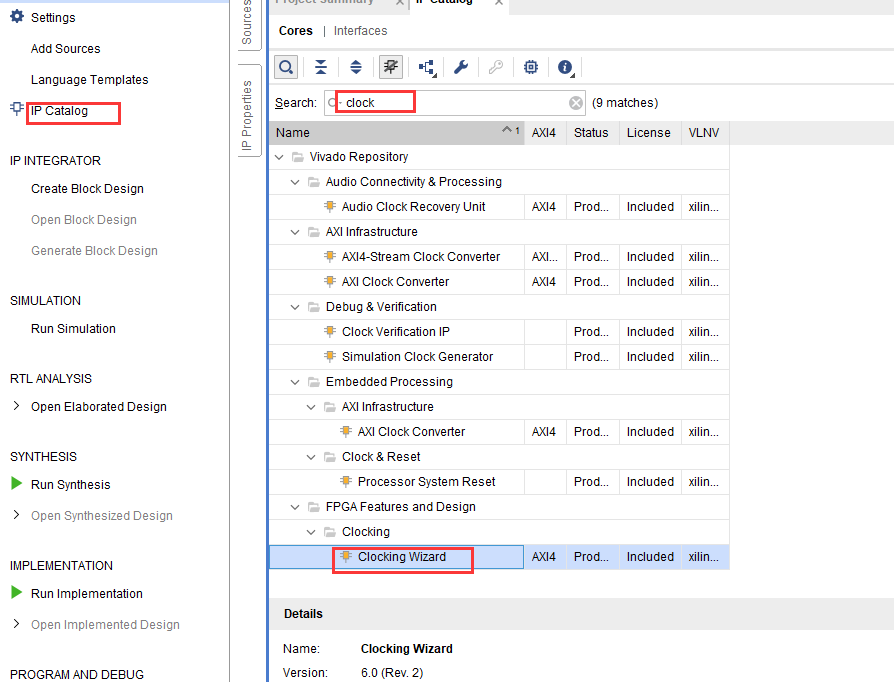

3. 添加新建完成 之后点击工程管理栏的PROJECT MANAGER下的IP Catalog,搜索clock,选择clocking wizard并 且双击,打开IP配置界面:

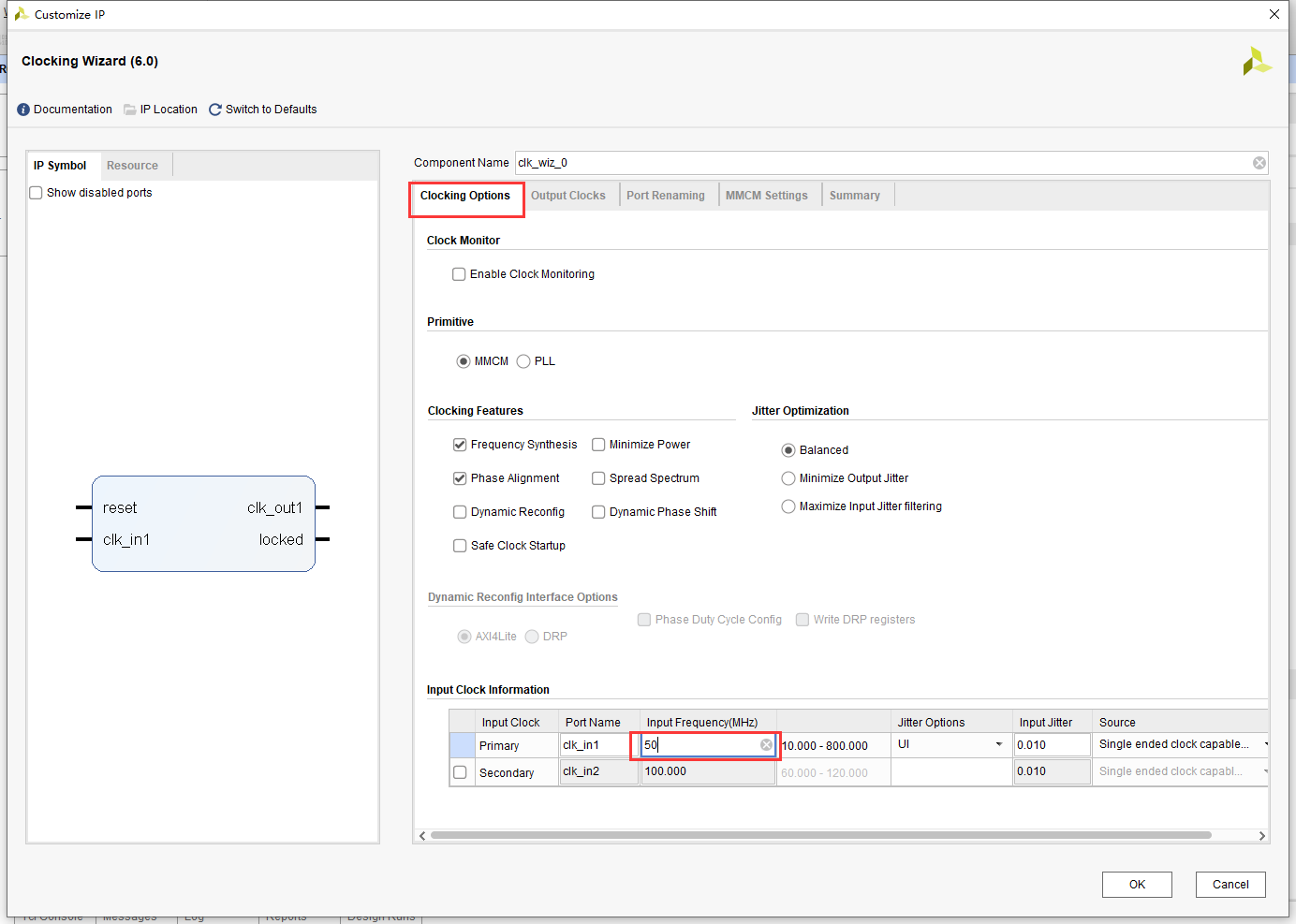

4.clk_in1设置为50MHZ

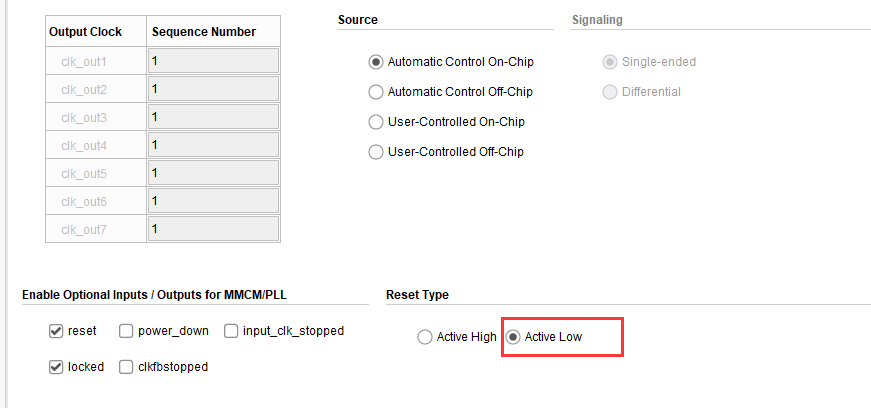

5. 下拉设置rest信号为低电平有效

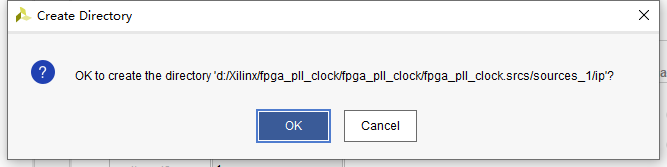

6.点击OK

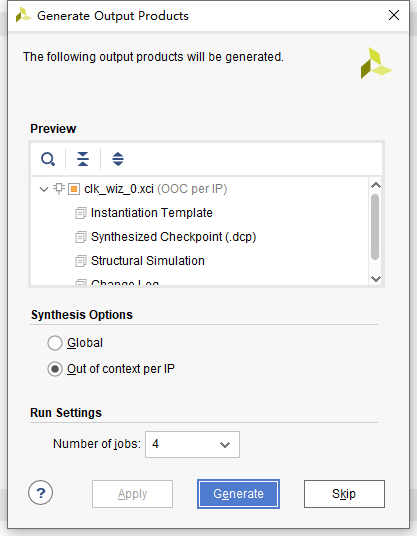

7.点击Generate

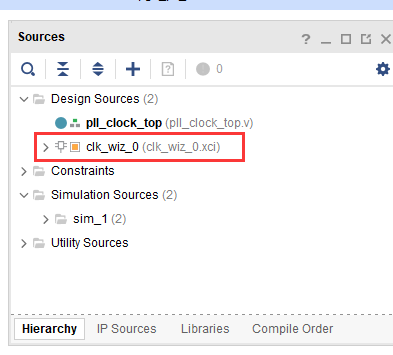

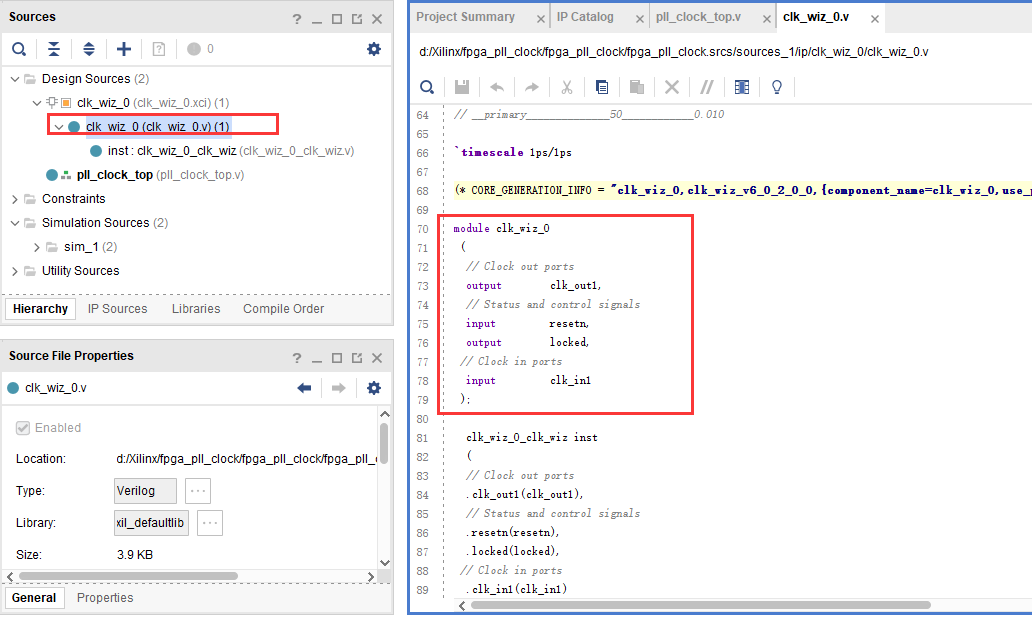

8.Design Sources出现了clk_wiz_0的IP核添加进来了。点击左边IP核的箭头,打开IP的架构。

9.点击OK

10.双击打开clk_wiz_0(clk_wiz_0.v),将这个时钟模块例化到pll_clock_top.v里面。

11.代码如下

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: yu meng ya

//

// Create Date: 2022/05/01 23:26:16

// Design Name: 锁相环时钟IP核

// Module Name: pll_clock_top

// Project Name: fpga_pll_clock

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module pll_clock_top(

output reg [3:0] led, // LED4 to LED1, 1 on, 0 off

input clk, // FPGA PL clock, 50 MHz

input rst_n // FPGA reset pin

);

wire clk_out1 ;

reg [31:0] cnt;

reg [1:0] led_on_number;

//clock input 50000000

parameter CLOCK_FREQ =50000000;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1;//change time 0.5s

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

cnt <= 31'd0;

led_on_number <= 2'd0;

end

else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin//计数0.5s

cnt <= 31'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end

always @(led_on_number) begin

case(led_on_number)

0: led <= 4'b0001;

1: led <= 4'b0010;

2: led <= 4'b0100;

3: led <= 4'b1000;

endcase

end

clk_wiz_0 clk_wiz_0_inst

(

// Clock out ports

. clk_out1 (clk_out1),

// Status and control signals

. resetn (rst_n),

. locked (),

// Clock in ports

. clk_in1 (clk)

);

endmodule

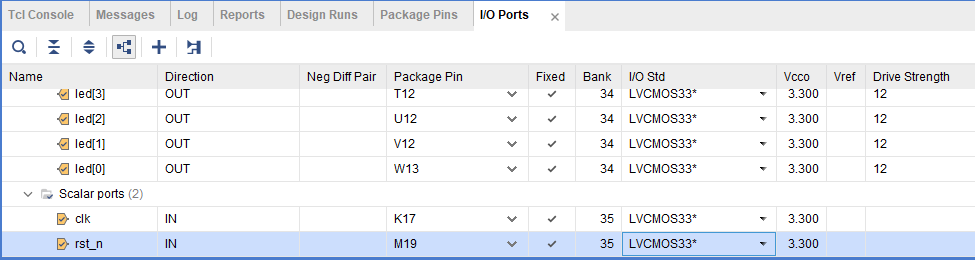

12. 先进行综合,然后引脚绑定

13.综合布局布线生成bit文件,下载到板子上。可以看到,流水灯比我们之前的实验效果要快一倍。因为 我们时钟倍频100M速度,而之前流水灯的时钟直接使用外部晶振,速度是50M。