核心思想:FPGA设计中的“物理”与“契约”

首先,要理解时序分析的本质。它不再是功能仿真中那个“逻辑对不对”的理想世界,而是进入了“物理定律说了算”的现实世界。

物理定律: 电信号在导线上传播需要时间(Tnet,网络延迟),通过逻辑门也需要时间(Tlogic,逻辑延迟),触发器响应时钟也需要时间(Tcq,时钟到输出延迟)。这些延迟是客观存在的物理事实。

设计契约: 我们通过时序约束(Timing Constraints),与EDA工具签订一份“性能合同”。我们告诉工具:“我设计的这个电路,必须要在100MHz的时钟频率下稳定工作!”

静态时序分析 (STA): EDA工具作为“合同审查员”,它不运行仿真,而是像一位经验丰富的工程师一样,拿出电路的“物理蓝图”(布局布线后的网表),根据每个元件和每段导线的延迟数据,通过数学计算来严谨地审查,我们的设计是否在物理上可能满足我们签订的“合同”。

第一部分:基本概念 - 触发器的“纪律”

一切时序分析都源于同步电路的基本单元——D触发器(Flip-Flop)。它有两个铁的纪律,所有人都必须遵守。

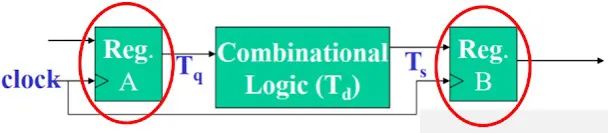

场景模型: 想象一个数据从源寄存器(Reg_A),经过一片组合逻辑(Combinational Logic),最终到达目标寄存器(Reg_B)。这两个寄存器由同一个时钟`clk`驱动。

1. 建立时间 (Setup Time, Tsu)

定义: 在时钟的有效边沿(例如上升沿)到来之前,目标寄存器`Reg_B`的数据输入端(D端)的信号必须保持稳定的最短时间。

比喻: 就像你要赶一趟火车(时钟沿),你必须在火车关门(时钟沿)之前就到达站台并站稳(数据稳定)。`Tsu`就是铁路部门规定的“必须至少提前5分钟到站”。

为什么需要: 触发器内部需要这点时间来“感知”并准备锁存输入的数据。如果数据在时钟沿附近变化,触发器就“看不清”数据是0还是1,从而导致亚稳态。

违反的后果:Setup Violation。这通常意味着你的组合逻辑路径太长(`Tlogic + Tnet`太大),或者时钟频率太高(留给数据传播的时间太短)。

2. 保持时间 (Hold Time, Th)

定义: 在时钟的有效边沿到来之后,目标寄存器`Reg_B`的数据输入端(D端)的信号必须继续保持稳定的最短时间。

比喻: 火车门已经关闭(时钟沿),你(数据)不能立刻离开站台,必须再多停留一会儿,确保你被火车系统完全、正确地识别。`Th`就是“关门后请在原地停留10秒”。

为什么需要:

确保触发器可靠地锁存了当前数据,防止下一拍的数据过早地到达,把当前数据给“冲掉”了。

违反的后果:Hold Violation。这通常发生在组合逻辑路径过短的情况下,导致时钟沿到来后,源寄存器`Reg_A`的新数据以极快的速度穿过组合逻辑,影响了`Reg_B`对旧数据的锁存。

3. 时钟到Q端延迟 (Clock-to-Q Delay, Tcq)

定义: 时钟有效沿到达后,寄存器的输出端(Q端)出现新的稳定值所需要的时间。这是触发器自身的内部延迟。

第二部分:静态时序分析 (STA) 的原理

STA工具就是基于上述概念,对设计中存在的千百万条时序路径进行逐一计算和验证。

1. 建立时间分析 (Setup Analysis) - “不要迟到”

这是对最长路径(Max Path)的分析,确保数据不会因为走得太慢而错过下一个时钟沿。

数据到达时间 (Data Arrival Time): 数据从`Reg_A`出发,到达`Reg_B`的D端总共需要多长时间?

`Arrival Time = Launch_Edge + Tcq + Tlogic_max + Tnet_max`

`Launch_Edge`: 源寄存器`Reg_A`的时钟沿(比如0ns)。

`Tcq`: `Reg_A`的固有延迟。

`Tlogic_max + Tnet_max`: 数据路径上最坏(最长)的逻辑和布线延迟。

数据要求时间 (Data Required Time): `Reg_B`最晚什么时候必须收到数据?

`Required Time = Latch_Edge - Tsu`

`Latch_Edge`: 目标寄存器`Reg_B`的捕获时钟沿(比如一个时钟周期后,10ns @ 100MHz)。

`Tsu`: `Reg_B`的建立时间要求。

建立时间裕量 (Setup Slack):

`Setup Slack = Required Time - Arrival Time`

Slack > 0: 满足要求。数据比要求的时刻提前到达了,裕量就是提前的时间。

Slack < 0:时序违例!数据迟到了,错过了捕获窗口。这个负值就是迟到的时间。

2. 保持时间分析 (Hold Analysis) - “不要早退”

这是对最短路径(Min Path)的分析,确保新数据不会变化太快,干扰到当前数据的锁存。

数据到达时间 (Data Arrival Time): 数据从`Reg_A`出发,最快能多快到达`Reg_B`的D端?

`Arrival Time = Launch_Edge + Tcq + Tlogic_min + Tnet_min`

这里用的是最短的逻辑和布线延迟。

数据要求时间 (Data Required Time): `Reg_B`的数据必须保持稳定到什么时候?

`Required Time = Latch_Edge + Th`

`Latch_Edge`: 捕获时钟沿(通常和Launch Edge是同一个沿,0ns)。

`Th`: `Reg_B`的保持时间要求。

保持时间裕量 (Hold Slack):

`Hold Slack = Arrival Time - Required Time`

Slack > 0: 满足要求。新数据在要求时刻之后才到达,旧数据得到了充分保持。

Slack < 0:时序违例!新数据太早到达,把旧数据冲掉了。

第三部分:时序约束 - 工程师的“指挥棒”

STA工具非常强大,但它不是万能的,它需要你来告诉它设计的意图和性能目标。这就是时序约束的作用。 约束通常写在专门的文件中(`.xdc` for Vivado, `.sdc` for Quartus)。

1. 主时钟约束 (`create_clock`)

作用: 定义设计中最基本的时钟信号。这是所有时序分析的起点和基准。

内容: 告诉工具某个端口(如`sys_clk`)上有一个时钟,它的周期是多少(如10ns),波形是怎样的(如50%占空比)。

示例: `create_clock -period 10.000 -name sys_clk [get_ports sys_clk]`

重要性: 没有主时钟约束,所有的时序分析都毫无意义。

2. 衍生时钟约束 (`create_generated_clock`)

作用: 定义由主时钟通过FPGA内部逻辑(如PLL, MMCM或逻辑分频)产生的新时钟。内容: 告诉工具新时钟与源时钟的关系(分频、倍频、相移等)。工具会自动处理这些时钟域之间的路径分析。

3. 输入/输出延迟约束 (`set_input_delay` / `set_output_delay`)

作用: 定义FPGA与外部芯片之间的时序关系。FPGA工具不知道外部芯片的特性,你必须告诉它。

`set_input_delay`: 告诉工具,一个输入信号在到达FPGA管脚时,相对于外部时钟,已经“飞”了多久了。这用来分析从FPGA管脚到内部第一个寄存器的建立/保持时间。

`set_output_delay`: 告诉工具,一个输出信号从FPGA管脚出发后,还需要“飞”多久才能到达外部芯片的寄存器,以及外部芯片的建立时间要求是多少。这用来分析从FPGA内部最后一个寄存器到输出管脚的路径。

4. 时序例外约束 (Timing Exceptions)

作用: 对某些特殊的路径,告诉工具不要使用默认的单周期分析方式。

`set_false_path`: 告诉工具某条路径是伪路径,不需要对它进行时序分析。例如,两个完全异步的时钟域之间的路径(在经过正确的异步处理后)、复位信号等。这是一个危险的命令,必须确保路径确实是假的。

`set_multicycle_path`: 告诉工具某条路径被设计为需要多个时钟周期才能完成。例如,一个计算模块的使能信号拉高后,需要3个周期才能出结果,那么从使能信号到结果寄存器的路径就可以设置为一个多周期路径。