使用SDK固化FLASH代码固化

一、实验目的:

实现对设计生成的bit流,固化到FPGA启动配置的FLASH内。固化后,上电即可自动配置bit文件,掉电不丢失。

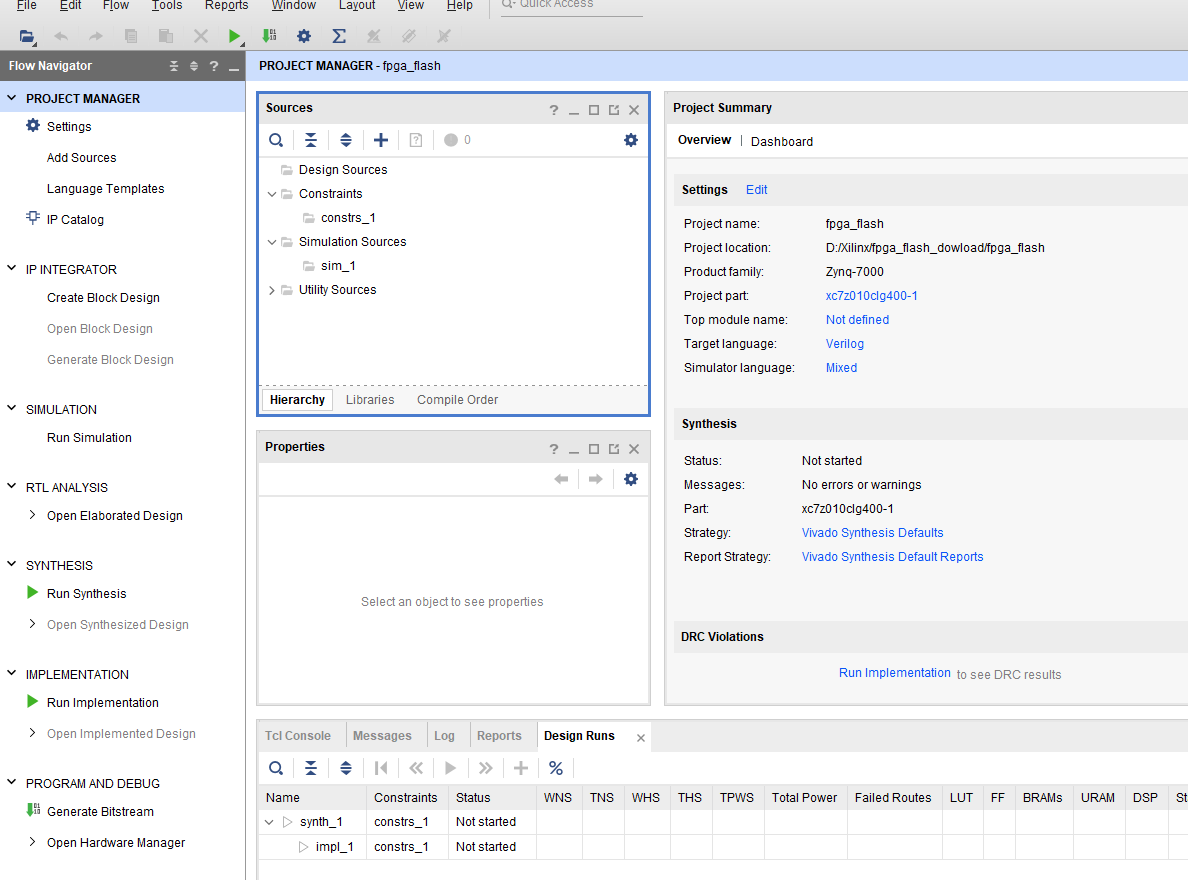

二、ZYNQ工程建立

三、固化前准备工作—ZYNQ处理器调用

ZYNQ芯片内部有ARM处理器,在上电的时候,由ARM运行一段启动代码,协助配置FPGA;并且,如果有软件代码,同时配置完成可运行软件代码。所以,我们需要用到ZYNQ芯片内的ARM处理器的模块。在ZYNQ芯片上,有一个处理器部分模块叫做ZYNQ7 Prosessing System的模块。此模块即是ZYNQ的处理器核心。跟DSP、门电路、加法器那些模块一样,可通过IP直接调用这个硬件。通过这个硬件的调用,我们就可以方便使用这个处理器,然后用XILINX的软件开发环境(SDK)新建处理器的软件引导代码即可完成ZYNQ的FPGA配置,引导代码可以通过新建工程模板实现,无需自己编写。最后将引导代码编译之后的可执行文件和bit文件一起打包烧写到FLASH即可完成我们需要的功能。

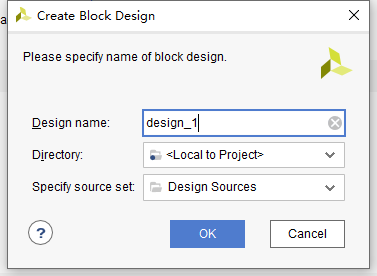

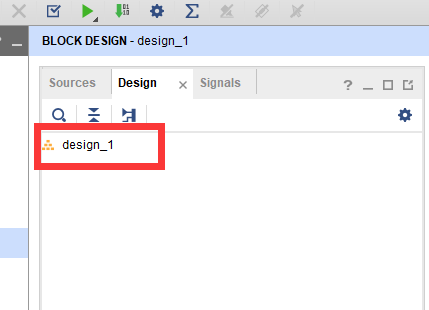

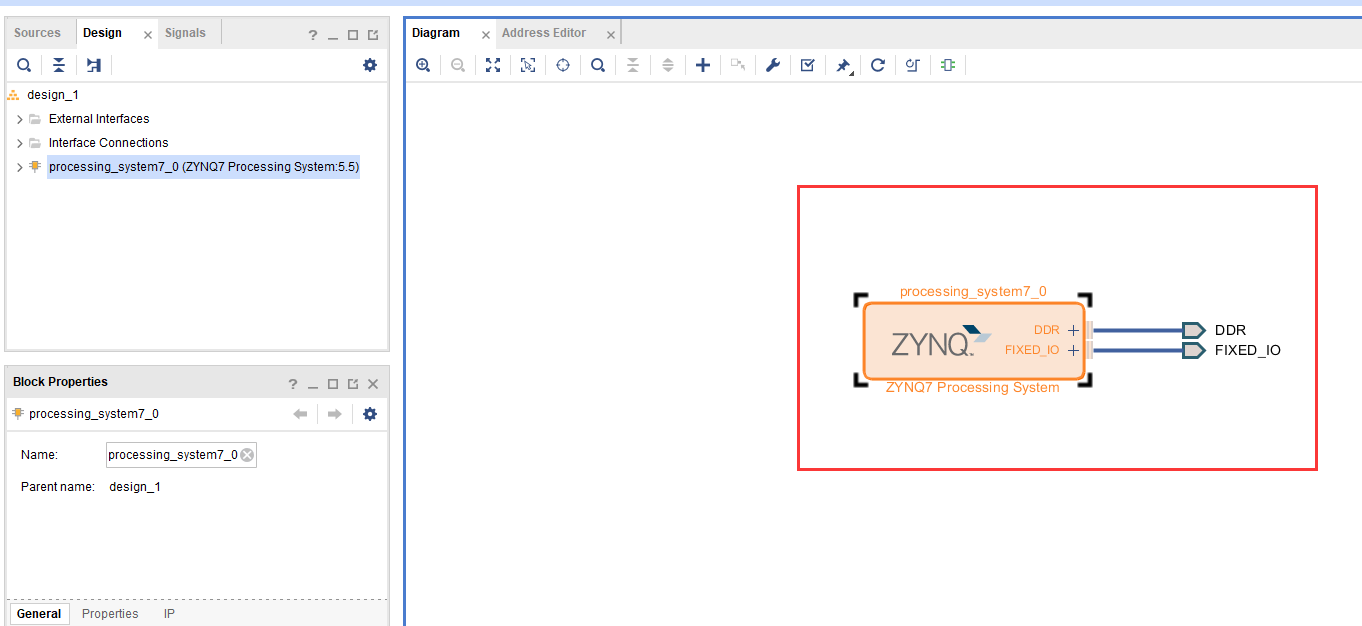

首先新建一个bd文件。IP INTEGRATOR下-->Create Block Design 点击创建bd文件,bd文件可以对FPGA图表原理图方式进行开发。

保持不变,点击ok

新建的bd文件

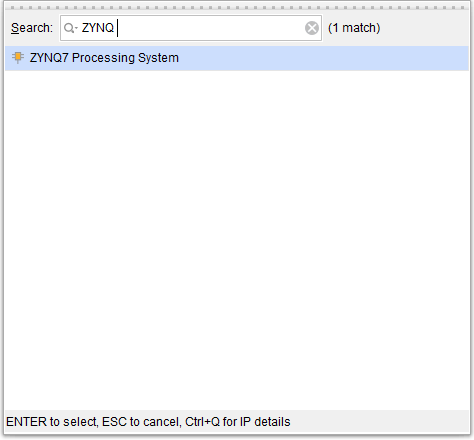

打开Diagram,点击+

输入ZYNQ,选择ZYNQ片上系统

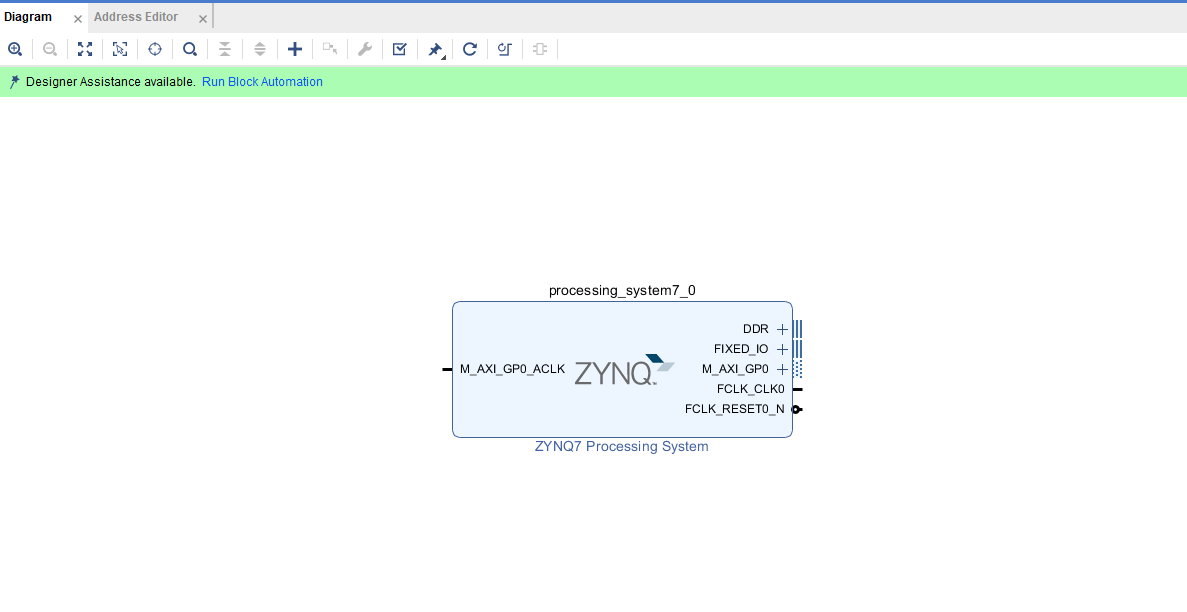

双击它,添加到bd文件中

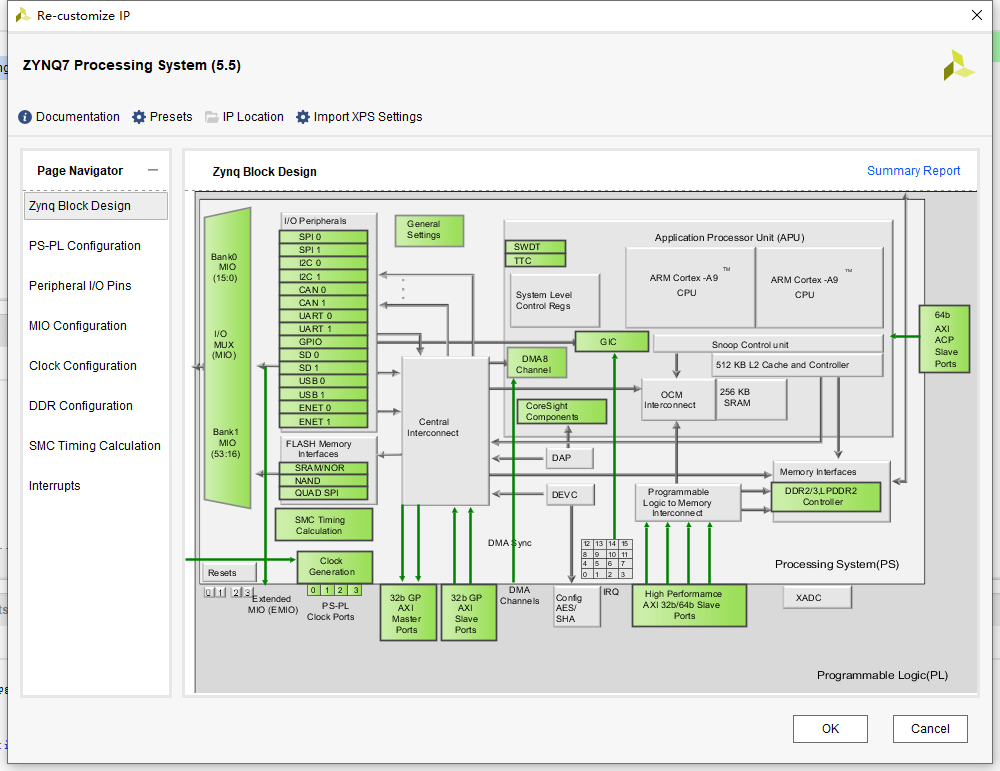

双击ZYNQ模块,打开IP配置界面,我们只需要将其配置成一个处理器最小系统,并且对芯片的FLASH引脚存储进行设置即可。

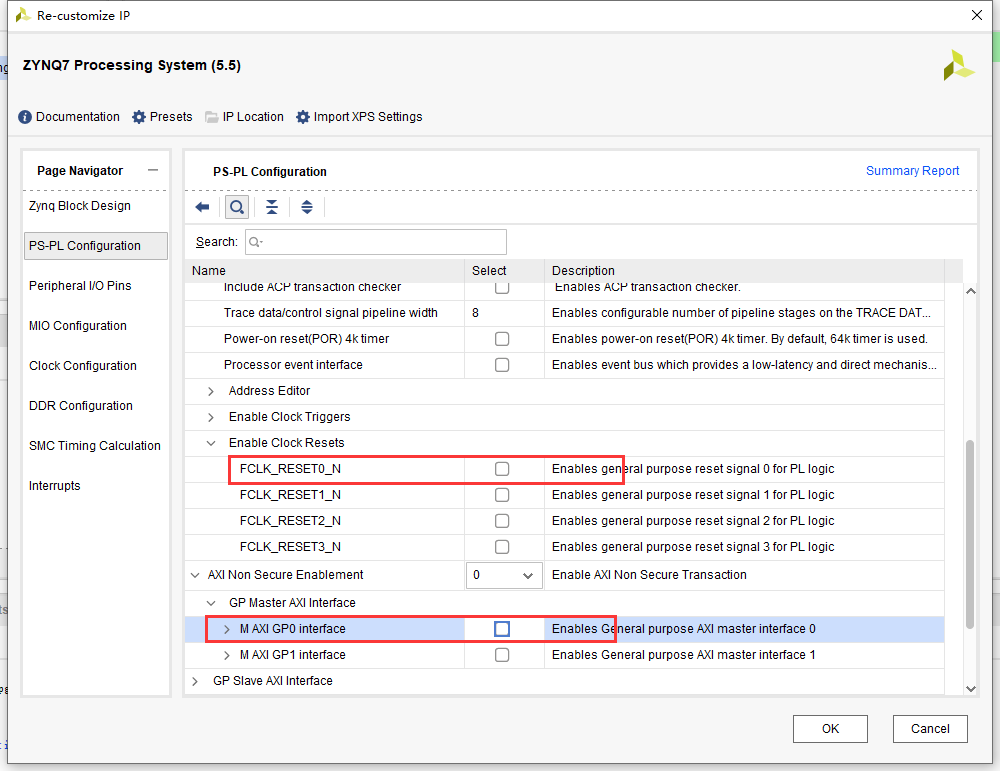

PS-PL configration的general,下拉找到enable clock resets,展开,将第一个 勾选掉,并且AXI Non Secure Enablement下的GP Master AXI Interface的M AXI GP0 interface勾掉

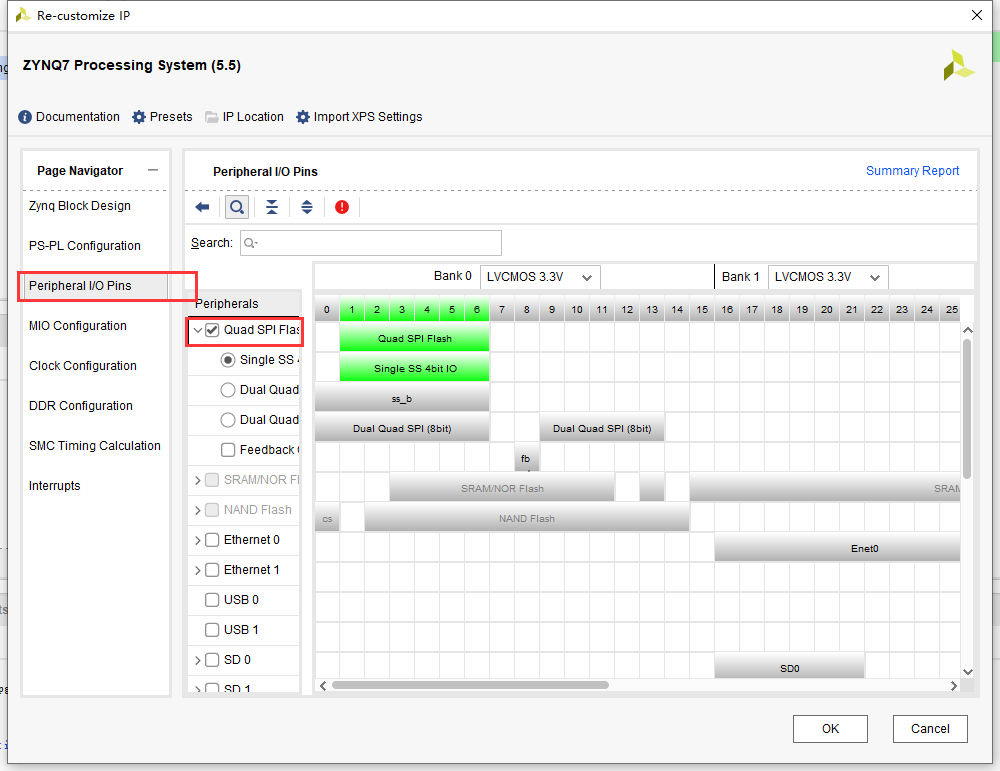

然后,在peripheral I/O Pins,选中Quad SPI Flash 勾选第一项:

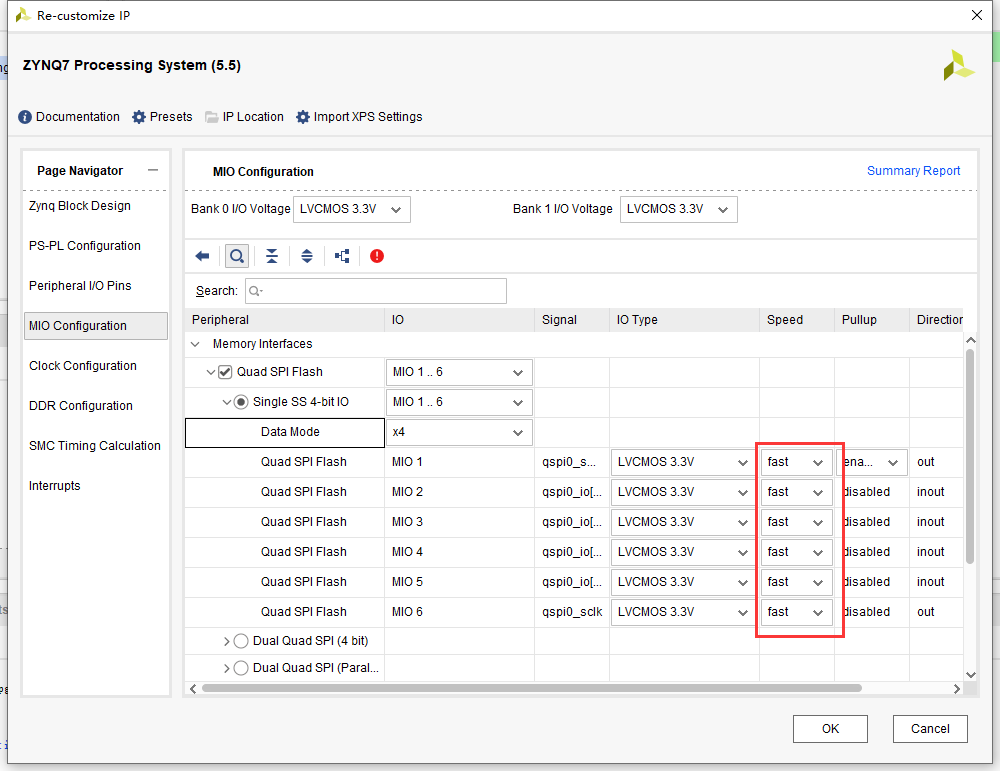

MIO Configuration ,展开Memory interfaces->Quad SPI Flash->Signle SS 4-bit IO,将speed改成fast:

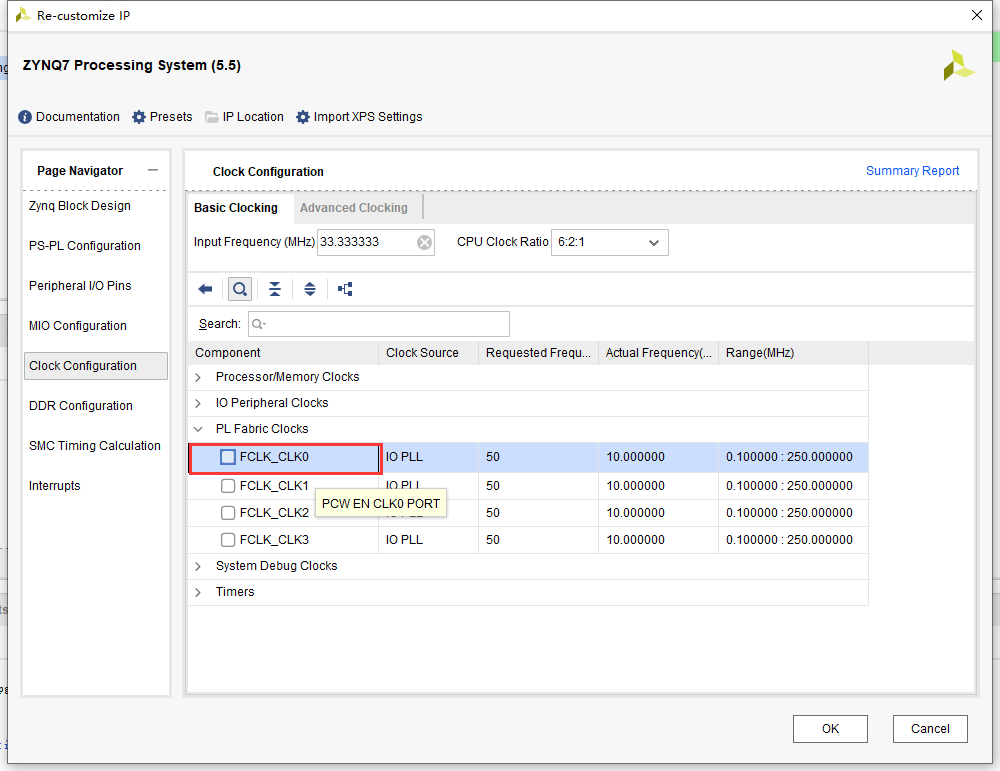

然后,Clock Configuration 勾掉PL Fabric Clocks下的 FCLK_CLK0:

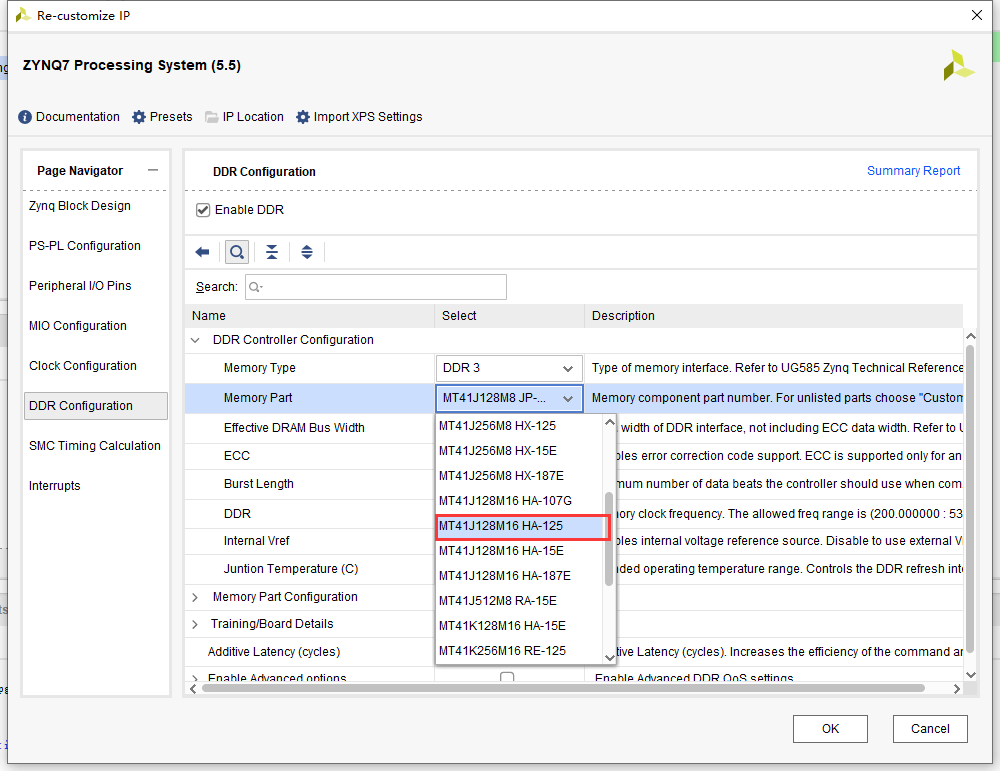

最后我们配置DDR3内存控制器,型号我们选择MT41J128M16 HA-125:

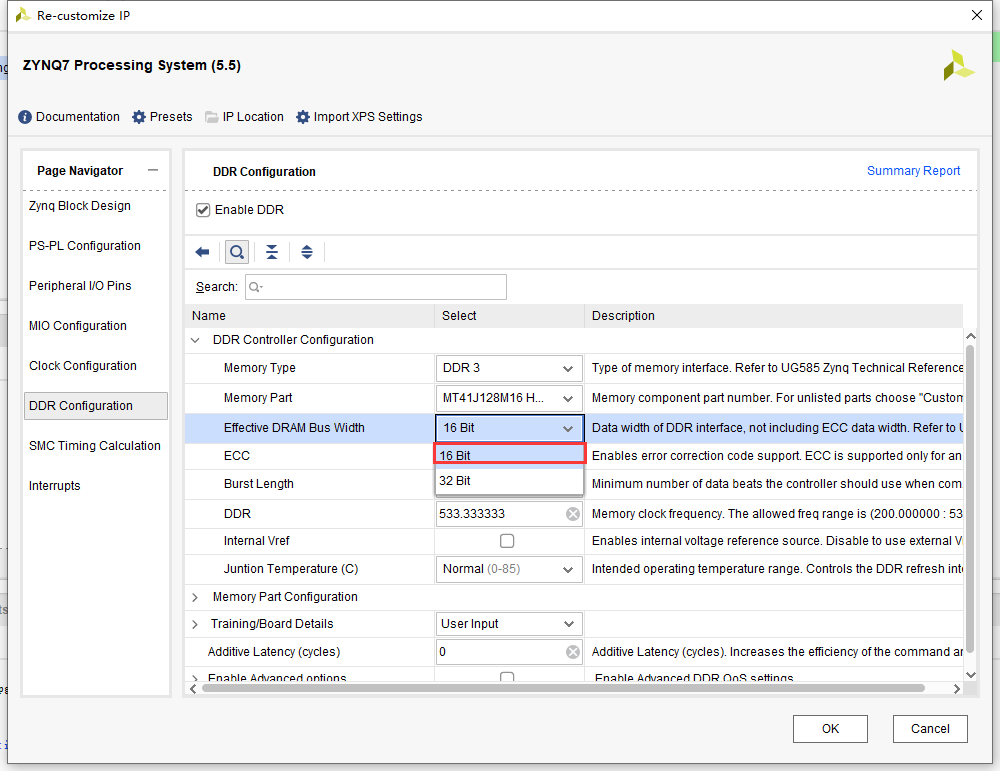

位宽选择16bit

最后点击OK,退出配置。

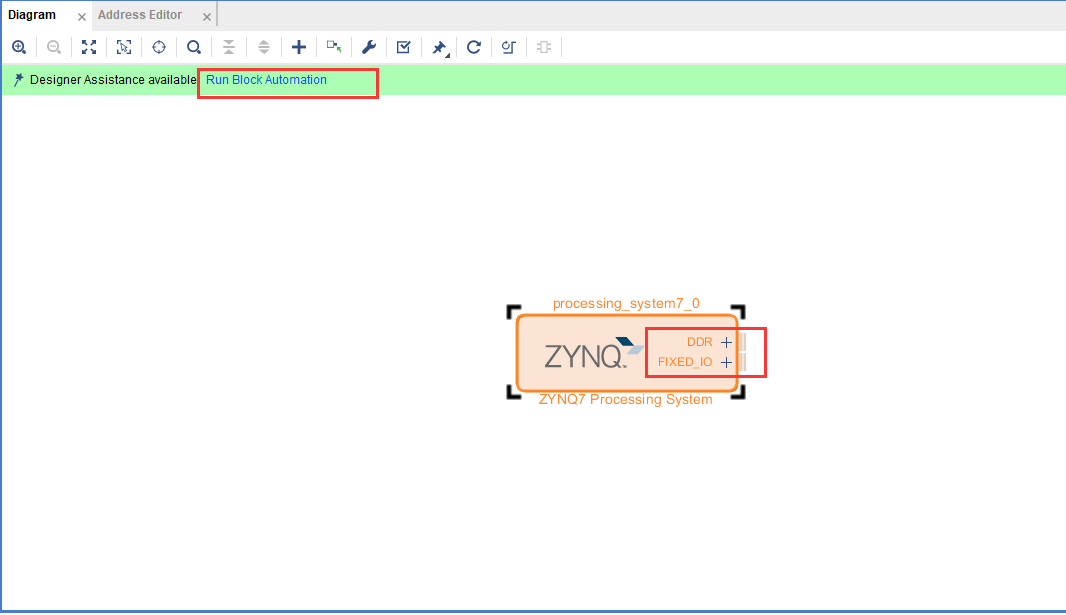

最后只剩下DDR和FIXED_IO。点击Run Block Automation

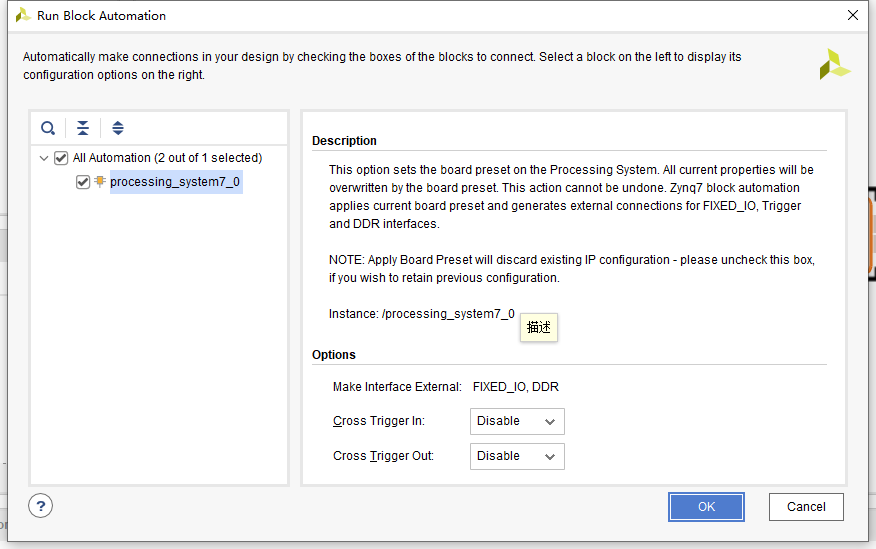

点击ok

最后,生成的模块图表IP变成了将DDR和FIXED_IP引出的状态

点击框框,将窗口最大化

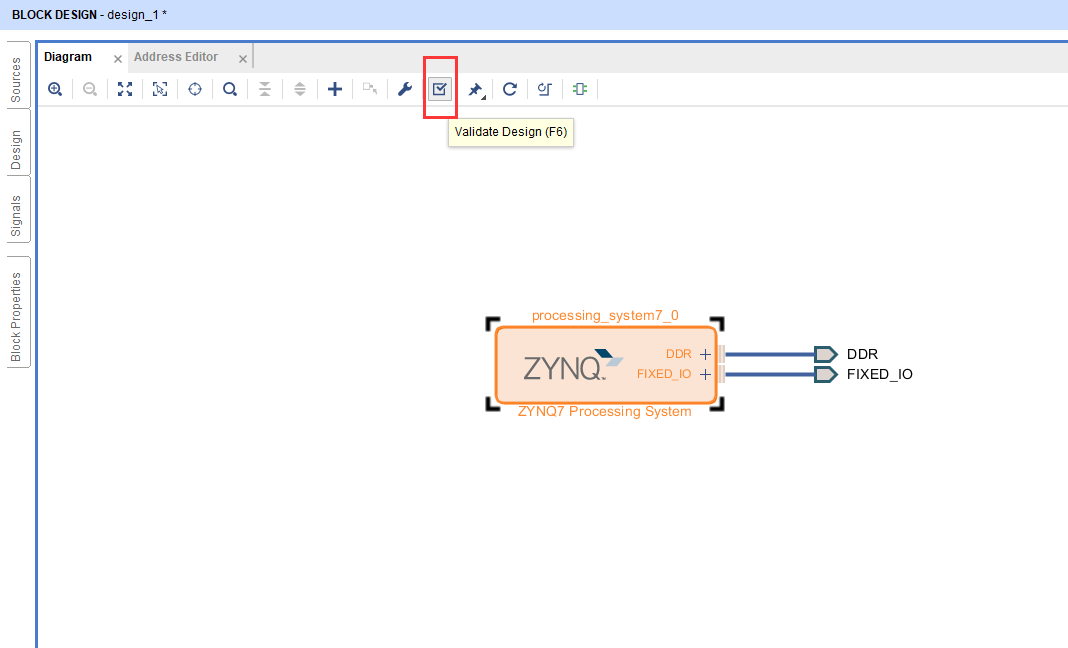

点击带有√的框框

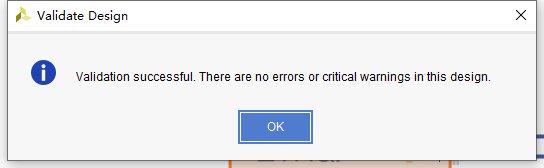

进行图表检查,点击OK

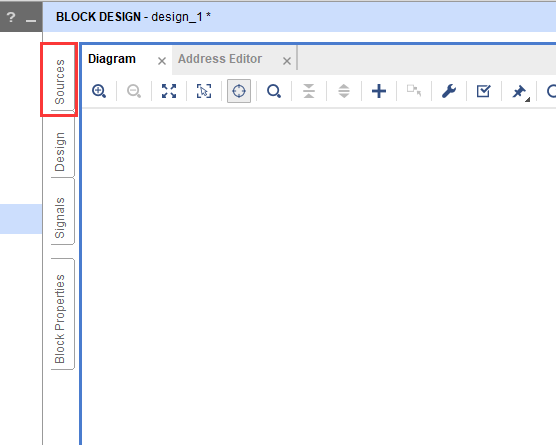

点击Sources

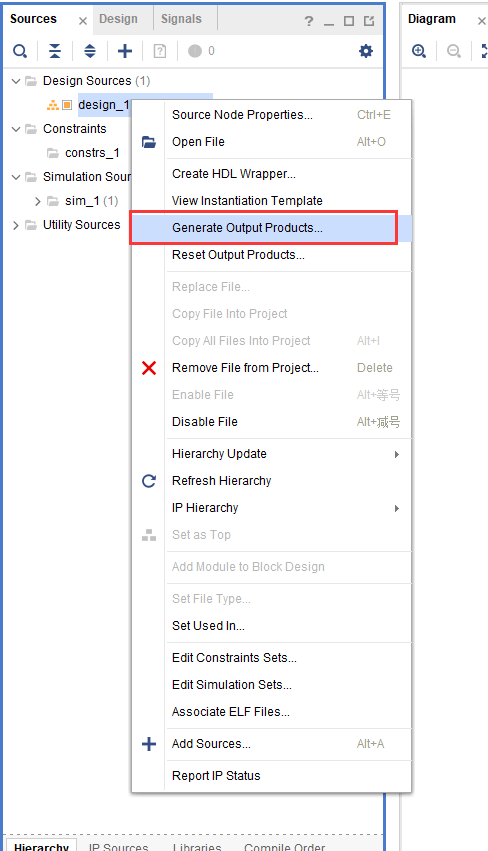

右键design_1文件,选择 Generate Output Products

点击Generate

点击OK

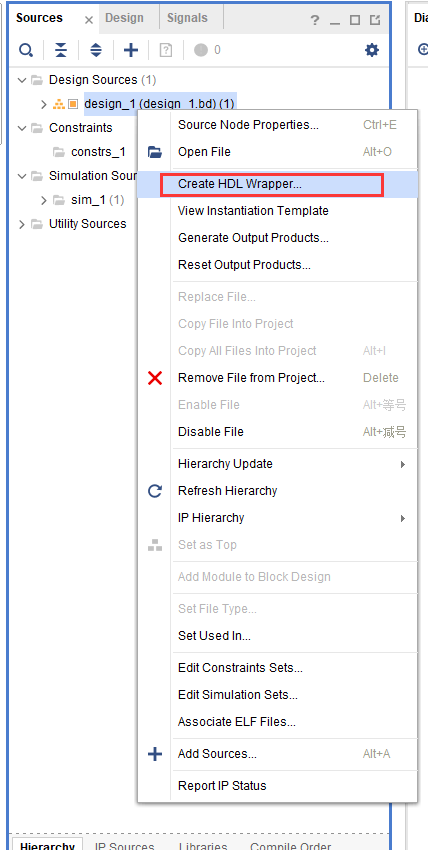

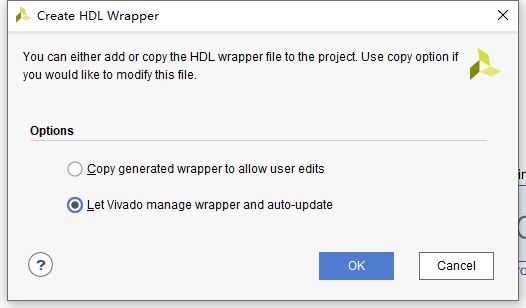

我们再次回到文件管理器,在bd文件右键,点击Create HDL Wrapper,生成顶层接口的 HDL文件,这个文件是我们的顶层模块HDL文件。

点击ok

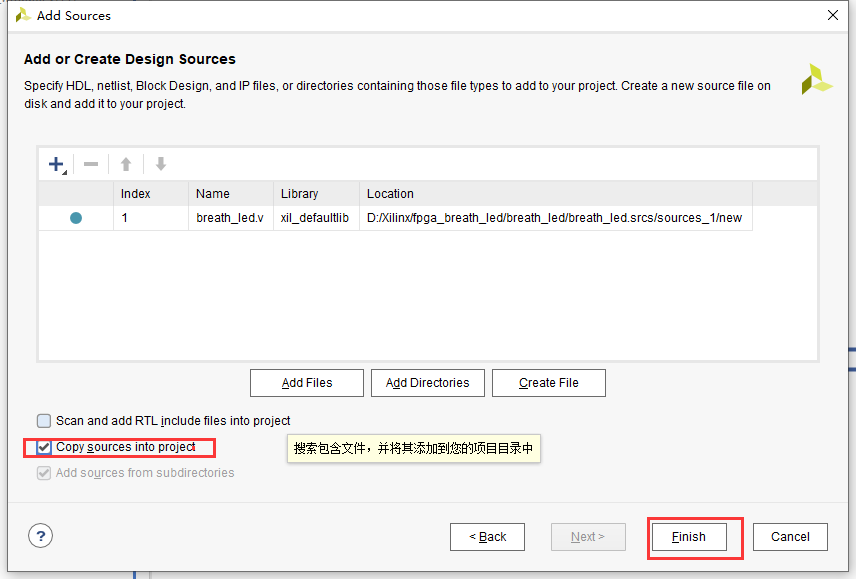

由于在ZYNQ处理器调用是直接调用模块,我们还需要在工程中自动生成的HDL顶层文件中例化我们的FPGA代码。我们将fpga_02_breath_led例程中的breath_led.v添加到工程中,Add Sources添加breath_led文件。

点击finish

添加完成

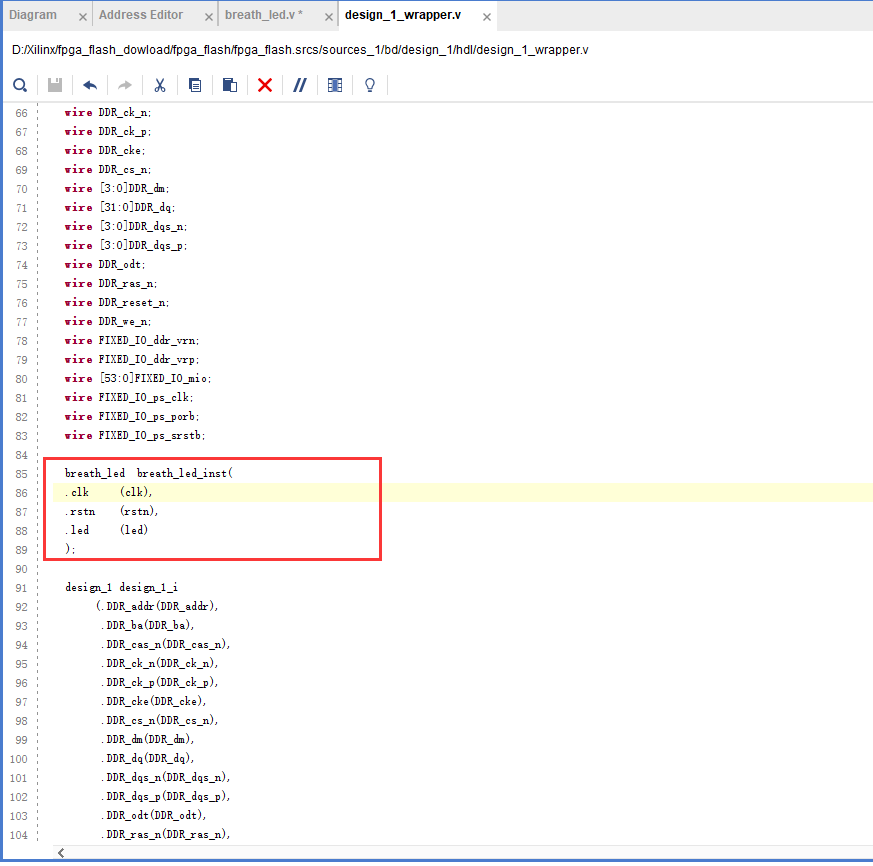

将breath_led.v里面的模块例化到design_1_wrapper。

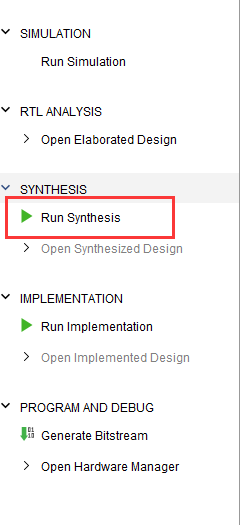

接下来进行综合

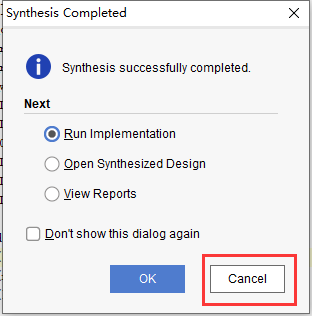

选择cancel

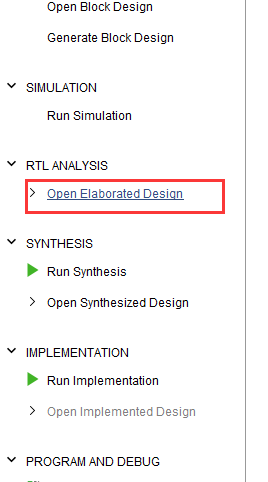

然后进行引脚绑定

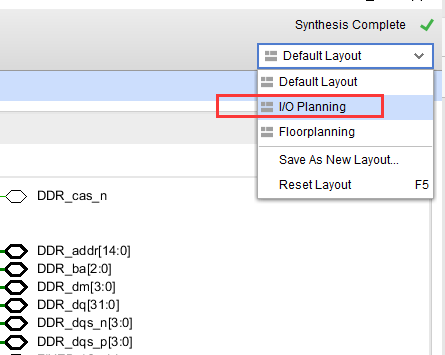

选择 I/O Planning

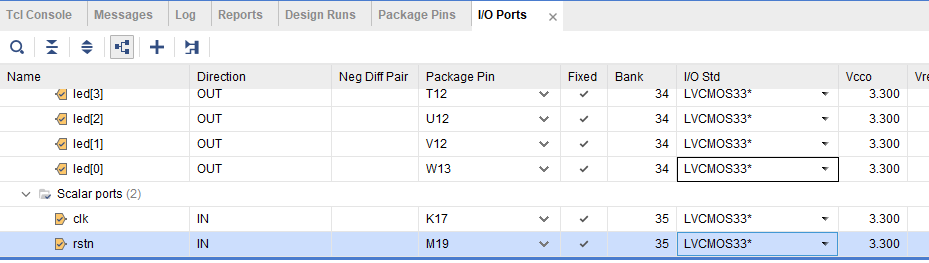

绑定引脚

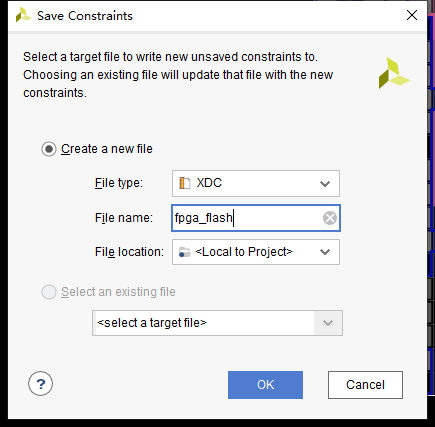

保存

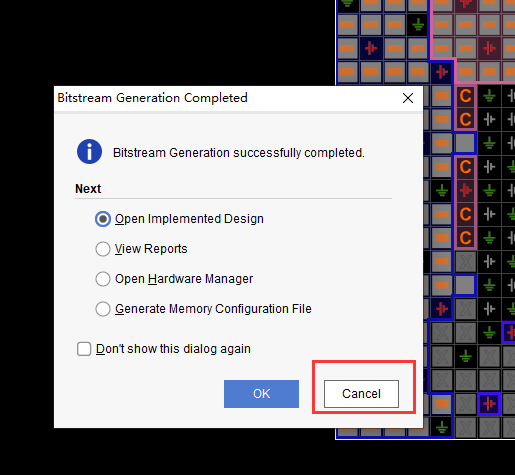

综合,布局布线,生成bit文件,等待完成。完成之后点击 Cancel:

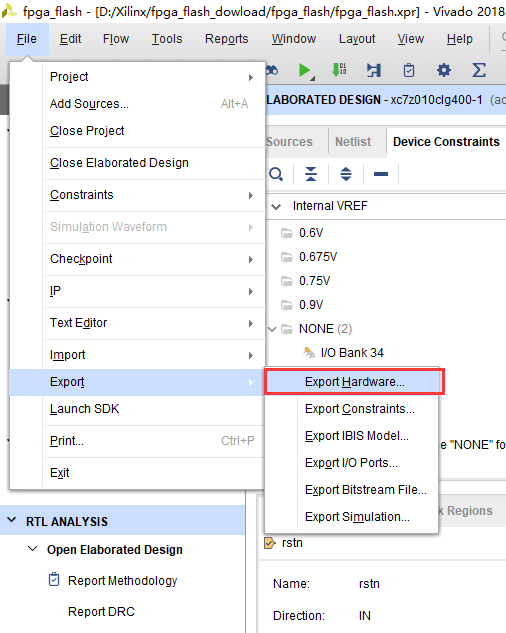

完成之后我们导出硬件描述文件。

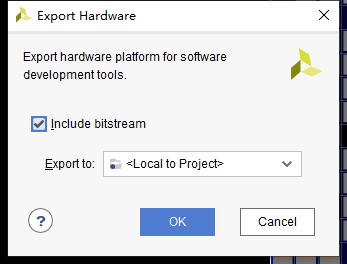

勾选上包含bit文件

四、新建FSBL的SDK工程及FPGA固化

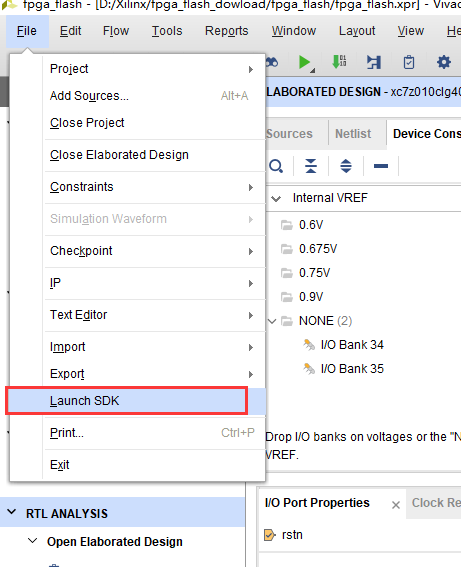

1. 我们回到软件主界面,最上面的工具栏点 击File->Launch SDK启动VIVADO的SDK开发软件。启动之后SDK会自动导入我们刚才定制

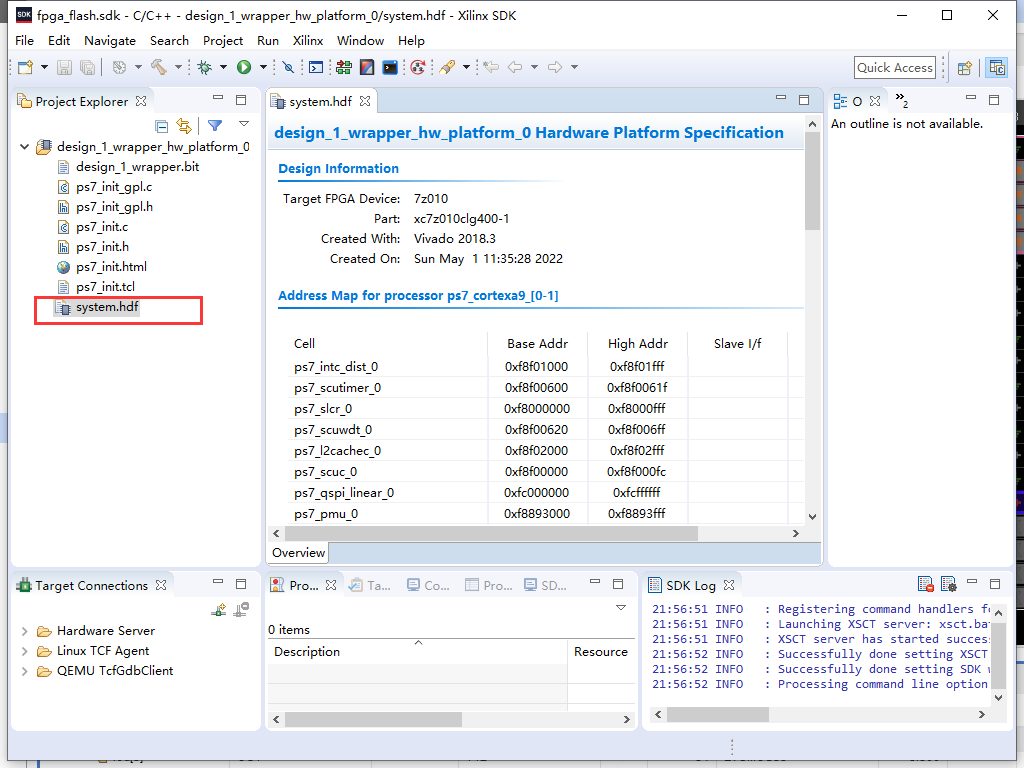

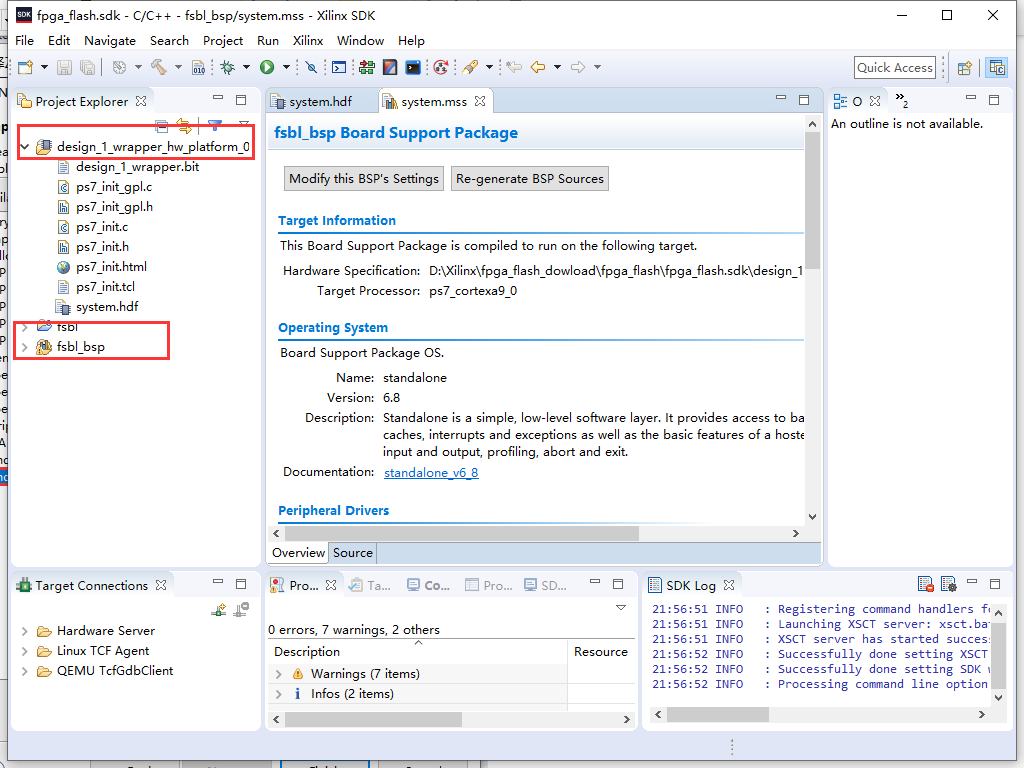

2. 启动之后,我们可以看见一个硬件描述代码工程

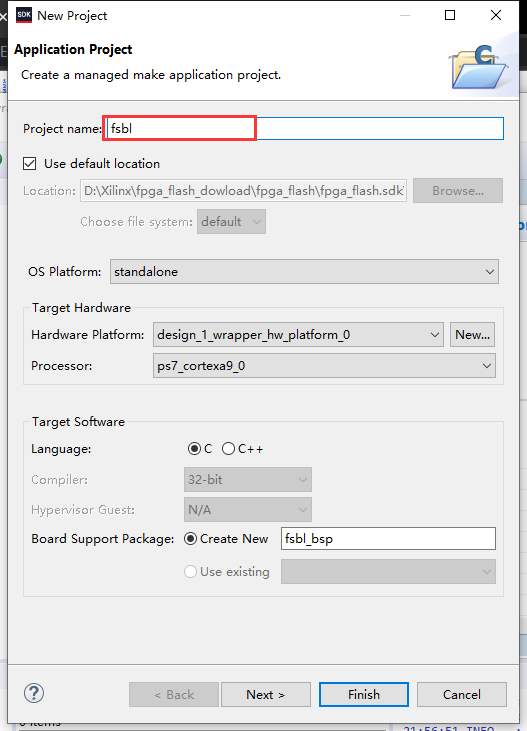

3. 我们在SDK新建一个启动引导工程:SDK最上方工具栏File->New->Application Project:

然后填入工程名,点击next

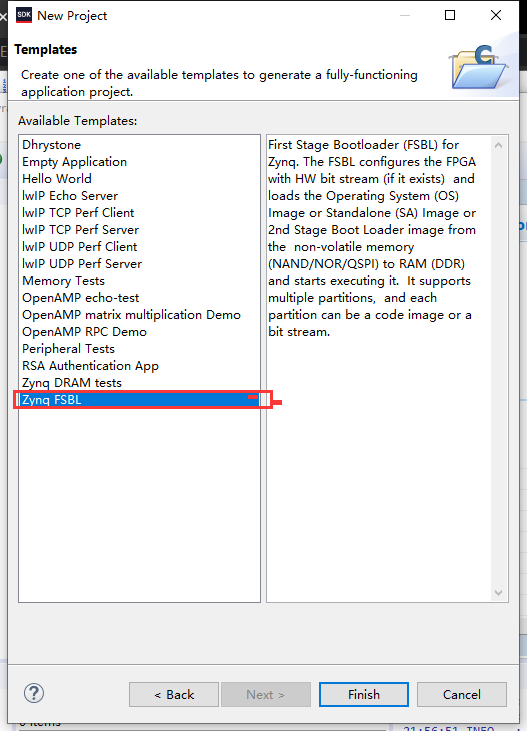

4. 选择ZYNQ FSBL,点击finish

5. 出现了三个工程,分别是硬件描述工程、fsbl启动引导代码工程、fsbl班级支持包工程

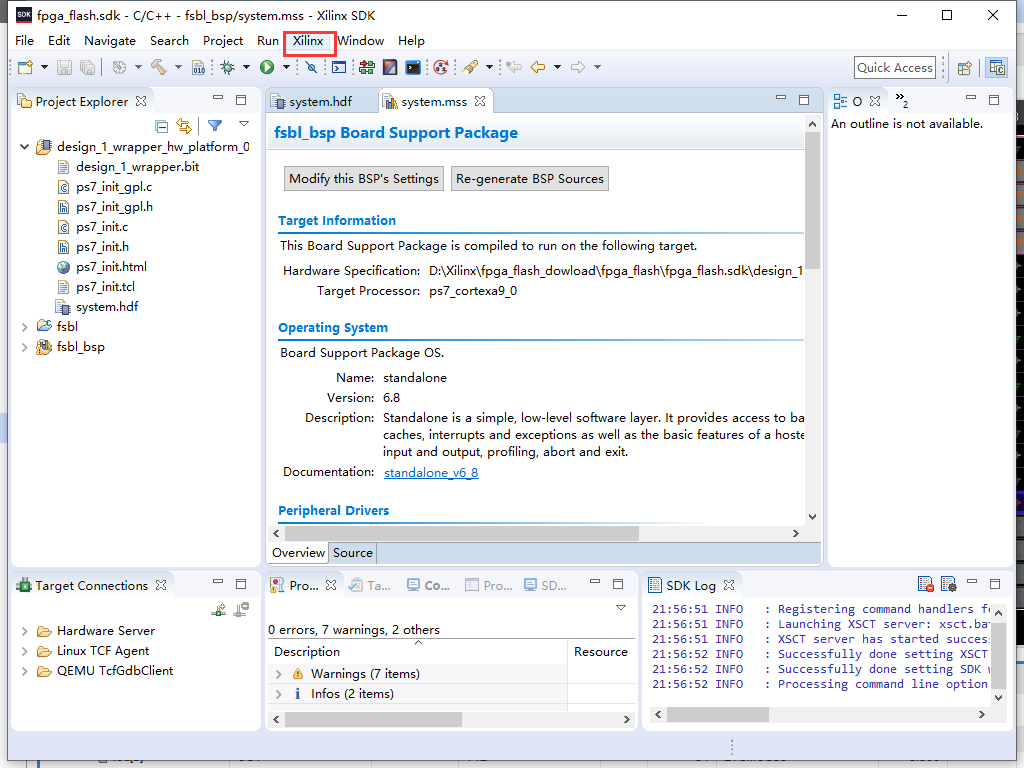

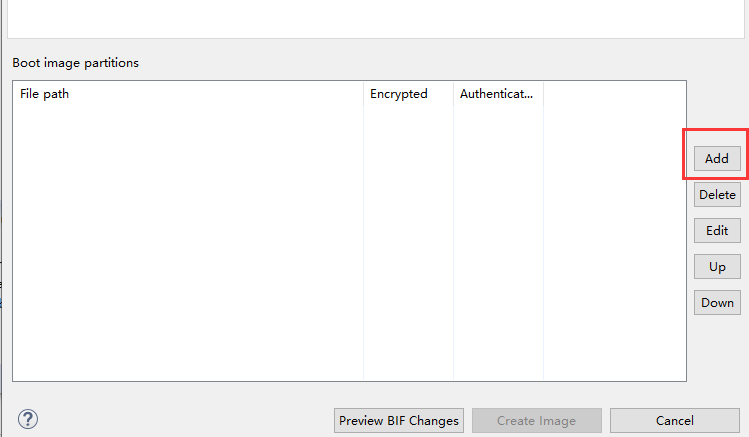

6. 到此,我们开始准备制作FPGA启动配置文件和固化到FLASH。我们点击SDK上方的工具栏中的XILINX->Create Boot Image,我们开始制作ZYNQ启动的bin文件

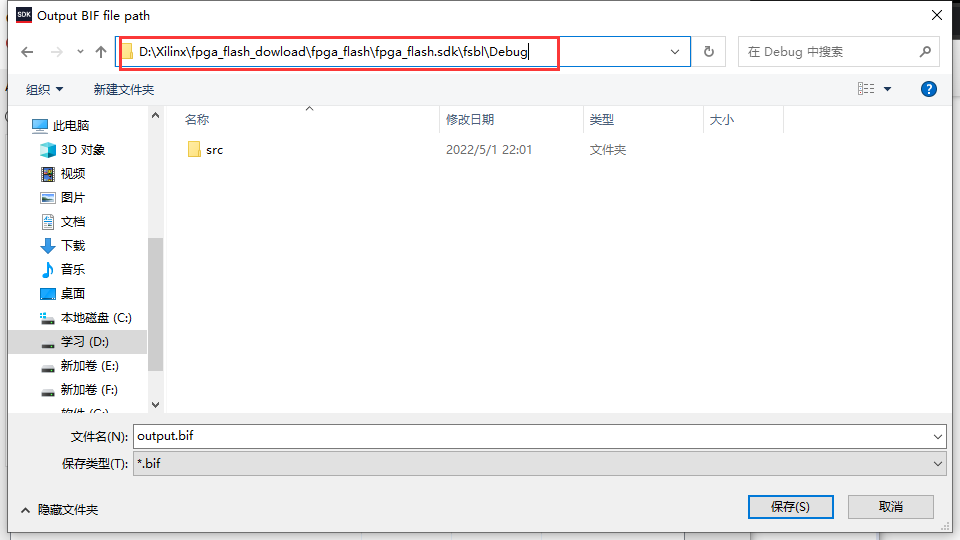

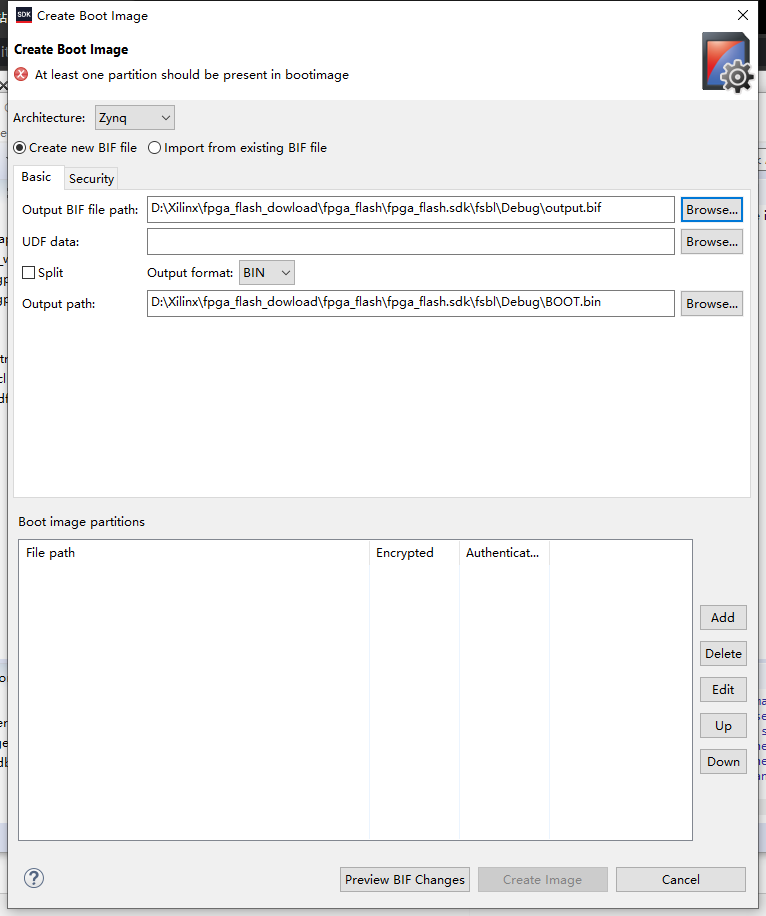

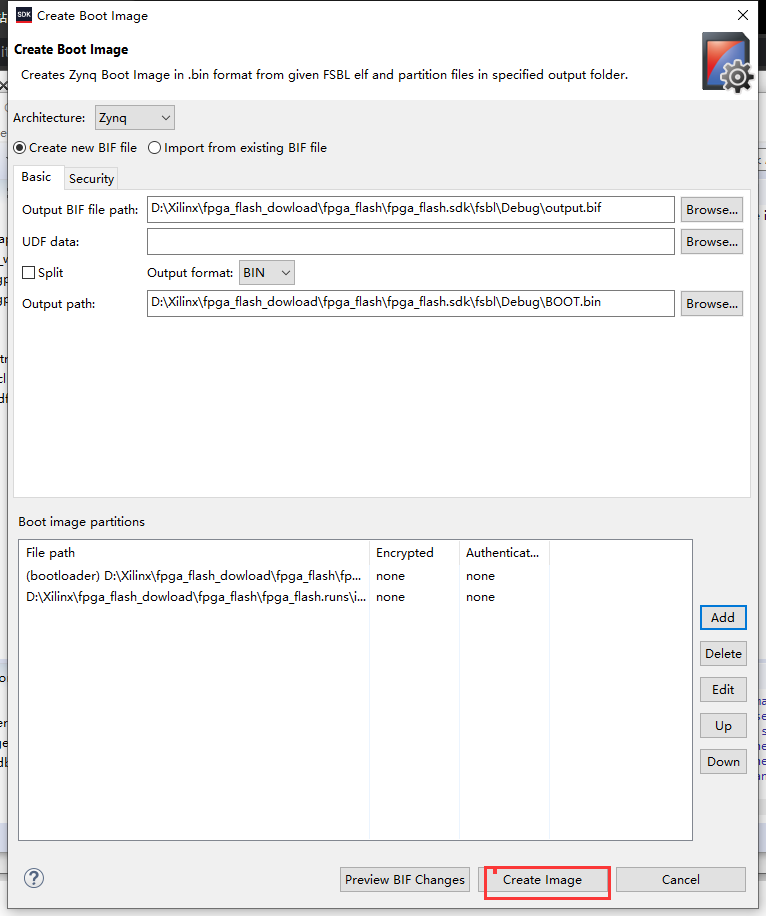

7. Output BIF file path配置输出生成的bif文件路径。 我们点击Browse,默认保存到工程的debug路径下面

8.保存路径为

9. Output path也默认在这个路径下,Output path即为输出的FPGA配置启动的BIN文件路径

10. 接着,我们添加文件。首先,我们添加fsbl启动引导代码生成的可执行文件,也就是我们 SDK新建的FSBL工程自动生成的arm可执行文件。

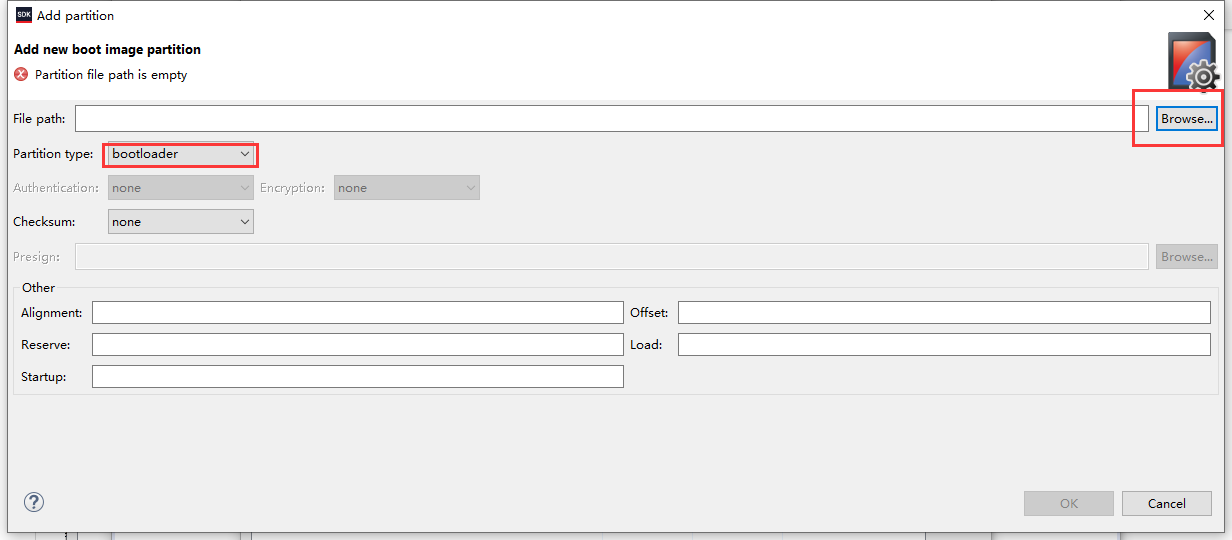

11. 点击弹出对话框中的browse进行选择注意Partition type默认是bootloader:

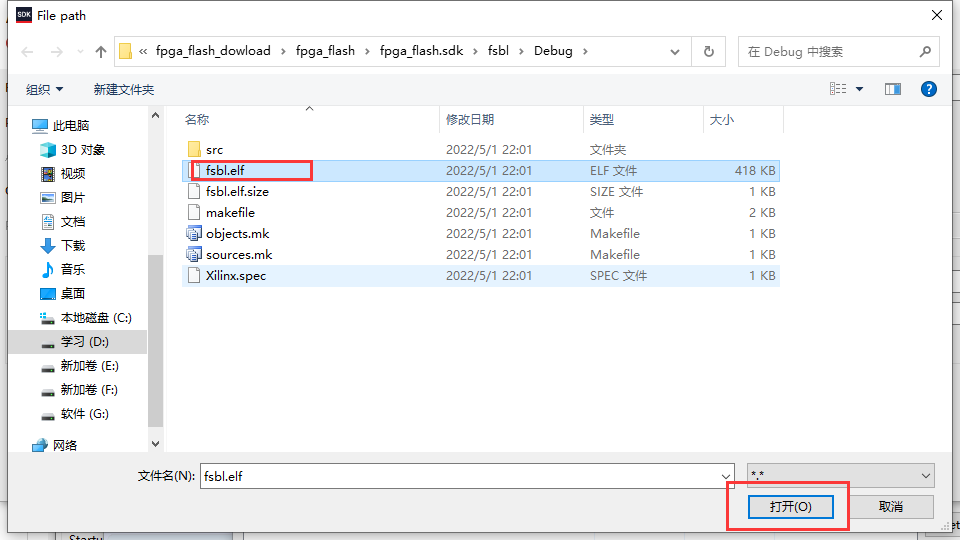

12. 选择fsbl.elf文件,点击打开

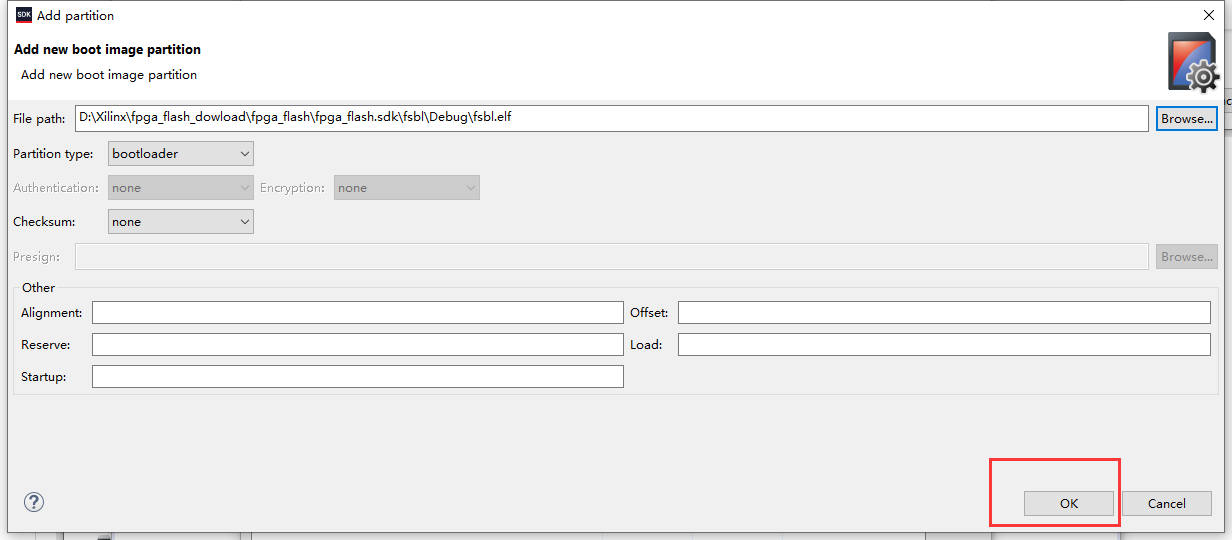

13 .点击OK

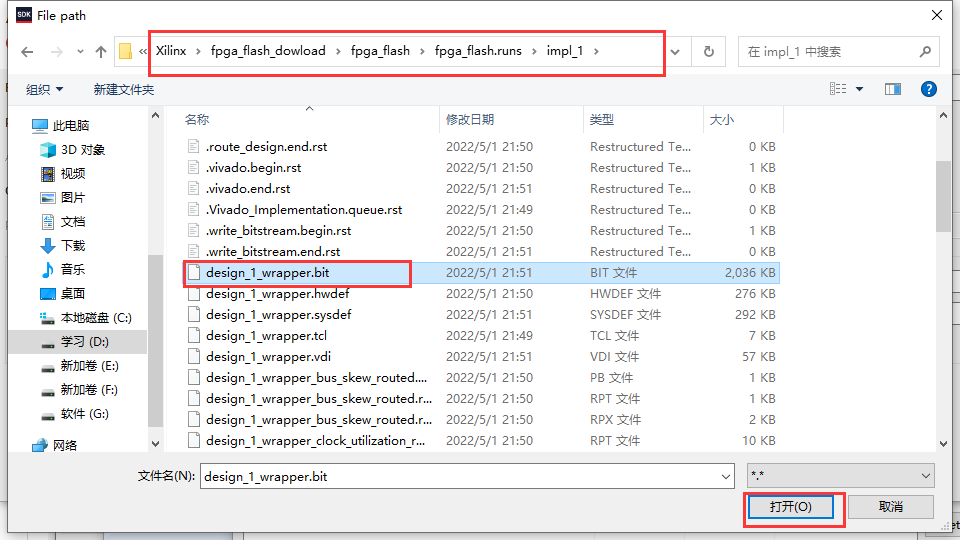

14. 再添加我们的比特文件。

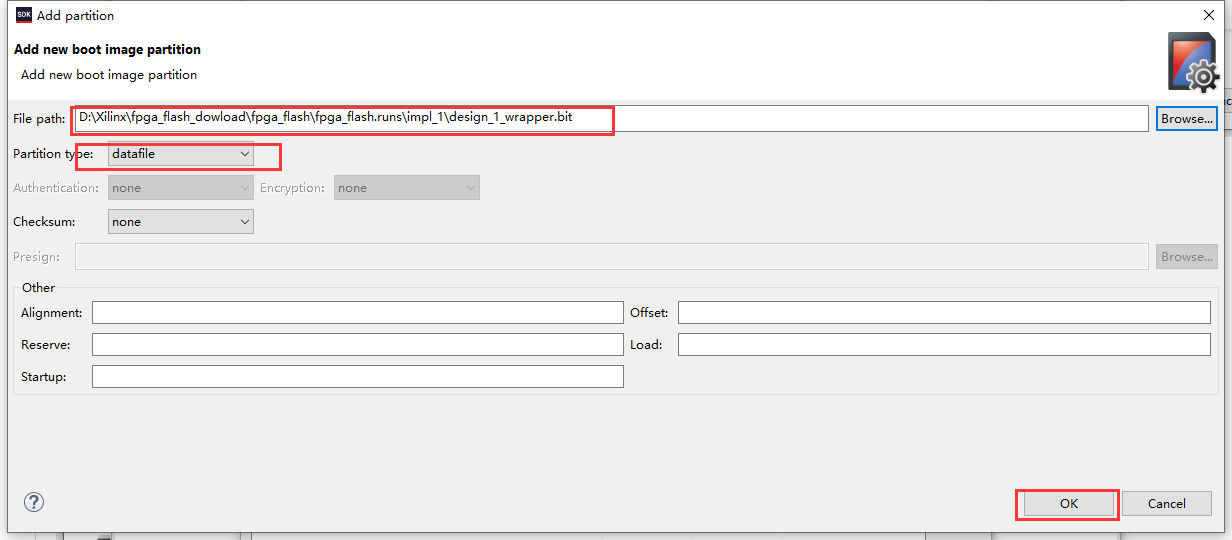

15.确定文件类型为datafile,点击OK

16. 一般制作启动BIN文件,都会先添加fsbl.elf文件,然后添加bit文件,如有ARM的代码app应用程序,还要添加一个app.elf文件,本工程只需要前两个文件。点击create image

17.到此BIN文件制作完成

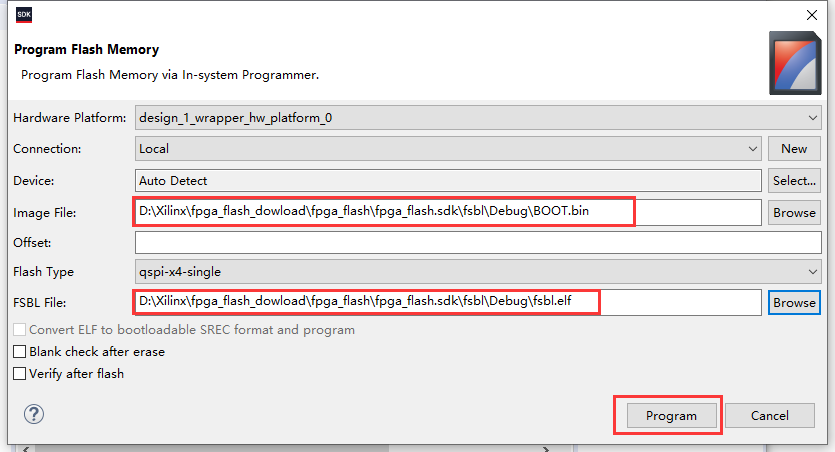

接下来我们开始固化。首先将拨码开关都置于ON状态。然后开发板插上USB线接到电脑,回到SDK,我们点击工具栏,点击XILINX- >Program Flash烧写。

Image 文件即刚才我们生成的BIN文件,FSBL即刚才选的FSBL.elf。然后等待FLASH操作 完成。

18.烧写完成之后,一定要断电重启。sdk烧写很慢,而且不好用。建议学习Vivado进行烧写。

本文 zblog模板 原创,转载保留链接!网址:http://xn--zqqs03dbu6a.cn/?id=45

1.本站遵循行业规范,任何转载的稿件都会明确标注作者和来源;2.本站的原创文章,请转载时务必注明文章作者和来源,不尊重原创的行为我们将追究责任;3.作者投稿可能会经我们编辑修改或补充。